For SoCs designed for various applications such as mobile, automotive, wearable computing, gaming, virtual reality, PC, imaging, security, and IOT applications, it is incredibly important to keep area (cost) and power as low as possible. Considering the growing percentage of chip area used for memory, it makes sense to choose the optimum memory IPs for each application. Among the memory IPs targeted for high-density consumer applications is the single-transistor dynamic random-access memory from Mentor Graphics (Novelics) called coolSRAM-1T.

You can read all about the coolSRAM-1T in Fundamentals of coolSRAM-1T Memory.

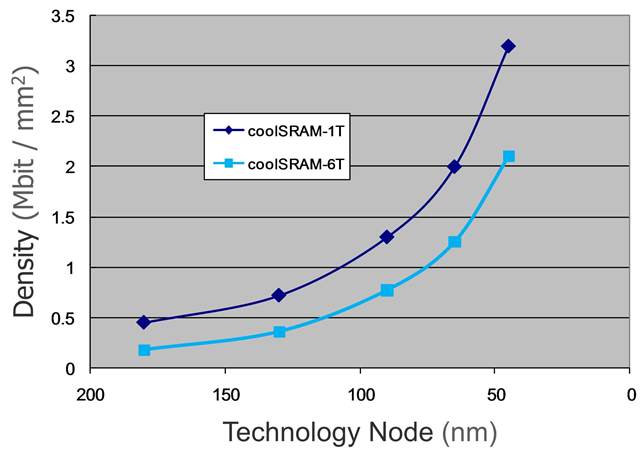

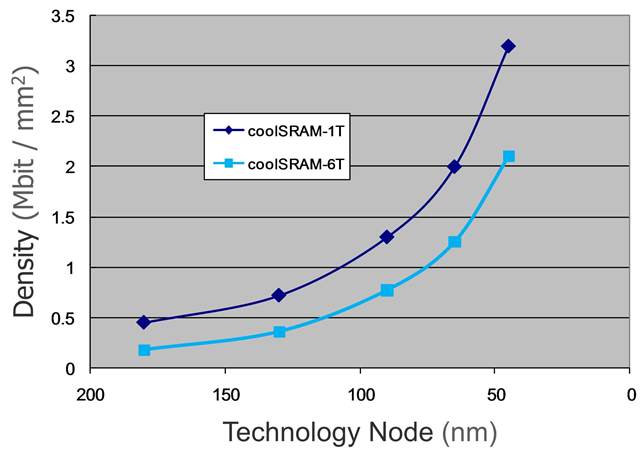

The one-transistor (1T) bit cell offers up to 50% reduction in core area for a given bit capacity compared to the more widely-used six-transistor (6T) bit cell. When your focus is on density over speed, the 1T architecture is an ideal choice. Figure 1 illustrates the density relationship between two embedded memory IP architectures.

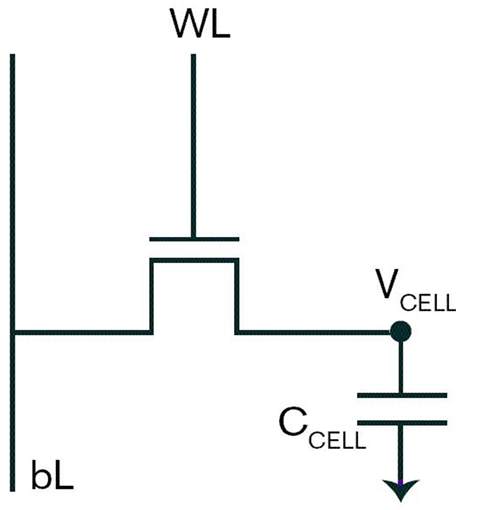

But what about static power for always-on SOCs? A 6T SRAM uses an active driver to maintain data, so leakage power can be a concern in advanced process nodes. The coolSRAM-1T uses passive storage structures optimized for low leakage. To minimize subthreshold and junction leakage, the Mentor Graphics’ coolSRAM-1T dynamic memory cell utilizes the thick oxide or input/output (I/O) transistor option available in all advanced process nodes. The coolSRAM-1T is a nearly seamless replacement for existing SRAM-6T for lower leakage and chip area. It is also cost-effective since it can be implemented using a bulk-CMOS process with no additional mask steps.

The peripheral circuits for the coolSRAM-1T include (1) the sense amplifier and (2) the write-back circuit that restores the charge into the cell after a destructive read. To boost the signal in a given cell capacitor area, we operate the cell array at I/O voltage, which results in a larger signal for the sense amplifier and improves performance. The interface to the system is at the VDD (core) voltage. The signals must be level-shifted from one voltage domain to another as they travel from the memory interface to the cell array, and we offer three approaches for doing that that offer different tradeoffs depending on your needs.

The coolSRAM-1T is integrated into the Mentor Graphics MemQuest compiler, the web-based tool suite that lets you specify and implement custom memories. Compiled instances in the 160nm 1.8V/3.3V, 130nm 1.5V/3.3V, and 110nm 1.2V/3.3V technology nodes have been incorporated into customer products and are in volume production and is also silicon proven in 65nm technology. With the IP license comes documentation about the test flow, which includes three major steps:

[LIST=1]

The coolSRAM-1T embedded memory IP is the only silicon-proven single-transistor SRAM IP that can be implemented in bulk CMOS. For high-density consumer applications, it can lower the overall system cost and static power consumption by reducing the area and the number of external components.

Learn more about Mentor Graphics coolSRAM-1T and the trade-offs between using the coolSRAM-1T and the coolSRAM-6T in this free Mentor whitepaper Fundamentals of coolSRAM-1T Memory.

Share this post via:

Comments

0 Replies to “1-T SRAMs in high-density, portable applications”

You must register or log in to view/post comments.