If your team is building large, complex designs that require millions of clock cycles to fully verify, you need both simulation and emulation.

If your team is building large, complex designs that require millions of clock cycles to fully verify, you need both simulation and emulation.

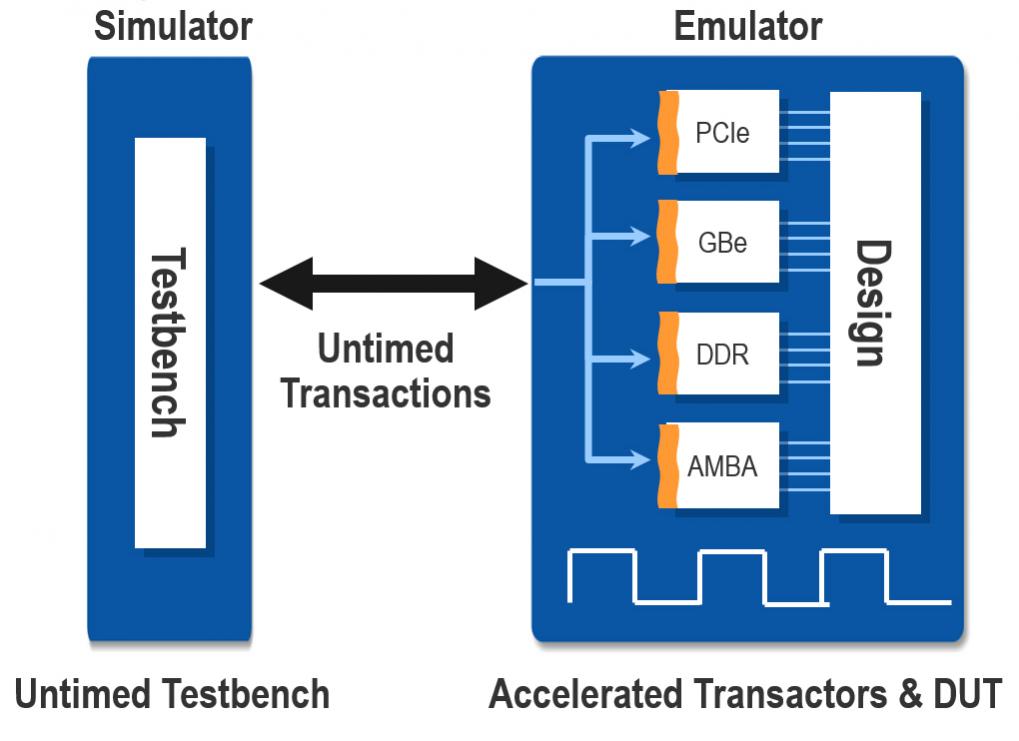

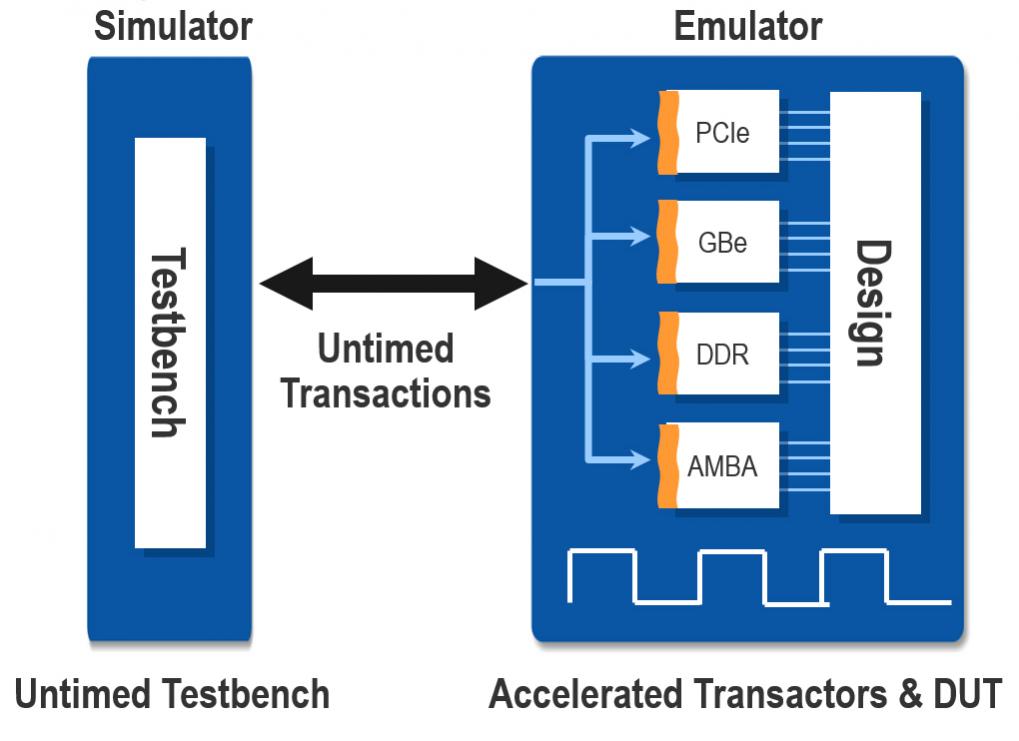

Using emulation with simulation accelerates performance for dramatically reduced run times.

Simulation brings higher modeling flexibility and functionality at the IP and block level. Emulation delivers enormous performance gains to the chip, sub-system, and full system level, including the ability to verify embedded software and hardware at the same time. Wouldn’t it be great if you could get the best of both worlds in a single, unified testbench environment that is reusable and moves with you from the block to system level, from simulation to emulation?

Well, you can, through a dual-domain testbench architecture and framework characterized by interoperability, flexibility and performance. Using this framework you’ll gain many benefits, principally:

- Increased verification performance and productivity

- Vertical reuse thru platform portability

- Reduced development effort

- Substantially lower design tape-out risk

Creating a unified testbench flow for both simulation and emulation, and reaping the benefits takes only three steps:

[LIST=1]

Sounds rather straightforward, doesn’t it? Indeed it isn’t intrinsically difficult, though there is a gotcha: you really should factor in emulation from inception of testbench development or else you’ll be creating a lot more work for yourself and your team.

Creating emulation-ready testbenches requires architecture considerations but performance benefits can be substantial. In emulation mode, large run-time improvements are made possible without sacrificing simulator verification capabilities and integrations such as modern coverage-driven and assertion-based techniques and tools. Imagine running a test that takes hours (or days) in a simulator in mere minutes with the added boost of an emulator. Imagine the number of design and testbench iterations that can be explored with these time savings. Imagine how much extra verification can be accomplished to further mitigate design risk.

So that you can better understand why this portable, unified, dual-domain framework for transaction-based testbench acceleration is powerful, we’ve put together a series of three papers that introduce the fundamental concepts and present the architectural and modeling requirements for SystemVerilog and UVM testbench acceleration using hardware emulation, and the steps to achieve optimal acceleration speed-up.

Reducing Design Risk with Testbench Acceleration

Part 1 in a series of papers that demystify the performance of SystemVerilog and UVM testbenches when using an emulator for the purpose of hardware-assisted testbench acceleration. In these three papers, architectural and modeling requirements are described, followed by a recommended systematic approach for maximizing overall testbench acceleration speed-up and achieving your ultimate performance expectations. This paper provides an overview of these concepts.

Testbench Acceleration Performance Demystified

Part 2 in a series of papers that demystify the performance of SystemVerilog and UVM testbenches when using an emulator for the purpose of hardware-assisted testbench acceleration. In these three papers, architectural and modeling requirements are described, followed by a recommended systematic approach for maximizing overall testbench acceleration speed-up and achieving your ultimate performance expectations. This paper discusses the components that constitute overall testbench acceleration runtime.

Optimizing Testbench Acceleration Performance

Part 3 in a series of papers that demystify the performance of SystemVerilog and UVM testbenches when using an emulator for the purpose of hardware-assisted testbench acceleration. In these three papers, architectural and modeling requirements are described, followed by a recommended systematic approach for maximizing overall testbench acceleration speed-up and achieving your ultimate performance expectations. This paper presents the recommended, systematic series of steps and guidelines for gaining overall testbench acceleration speed-up and achieving performance expectations.

Comments

There are no comments yet.

You must register or log in to view/post comments.