One of the most energetic presentations at the recent TSMC OIP 2015 symposium was given by Tom Williams from Qualcomm, who shared his insights (and enthusiasm!) for Mentor’s Calibre RealTime interactive Design Rule Checking (iDRC) product.

Paraphrasing Tom’s presentation (and with a tip of the hat to David Letterman), here is a list of the Top 10 reasons to invest in iDRC verification, with a tool such as RealTime.

(10) Design rules have become incredibly complex – the days when the (majority of) rules could be memorized are long over. The rule descriptions are also very complex, necessitating visual feedback. Interactive DRC tools support the full DRC runset.

Tom W. highlighted that the Design Rule Manual (DRM) for TSMC 16FF+ devotes 80 pages to the MEOL layers alone. 🙁

(9) Using a connectivity-driven schematic model, layout “gen-from-source”, and parameterized layout cells (with abutment and merging support) does greatly assist layout designers. Yet, the rule complexity in #10 above suggests that correct-by-construction for cell/macro layout composition is extremely difficult to achieve – a fast verification method is still required.

(8) Multi-patterning verification requires color assignment to be exercised, and (complex) cyclic errors to be highlighted. These decomposition algorithms are far beyond traditional width/spacing/enclosure checks, and demand automation.

(7) The performance of iDRC tools provides fast turn-around time. It completely replaces the traditional interactive method – i.e., “pop up a ruler, measure, and compare to the DRM”.

There is a caveat, to be sure, on the size of the layout macro that is suitable for iDRC. Tom W. indicated that the Calibre RealTime guideline is to work with a layout cell with less than 3 million shapes.

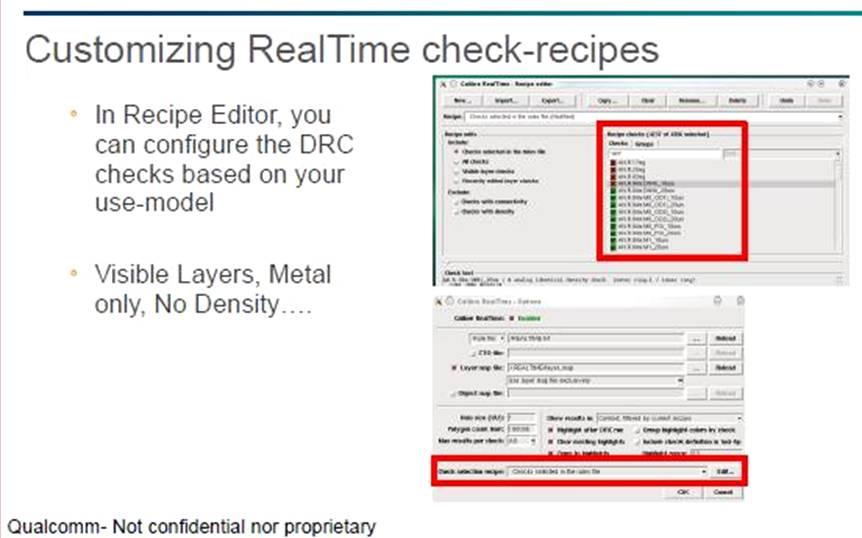

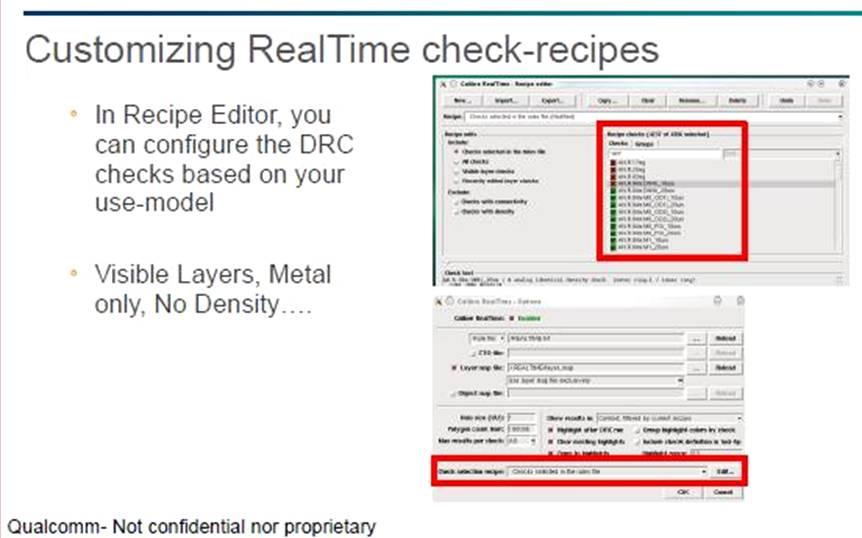

(6) RealTime performance can be further enhanced by using the “Recipe Editor”, as shown in the figure. iDRC can be quickly configured to define a subset of rules and/or layers that will be presented to the checking engine.

Tom W. provided the example of “density checks” as a rule subset that would typically be excluded from RealTime verification during initial layout composition.

(5) The computational resource applied to iDRC – typically, a local workstation or a remote login server dedicated to interactive applications – alleviates the “server farm” from this resource demand. There’s no need to streamout, then submit, queue, dispatch, track, and write report files from batch DRC jobs, a workload which can otherwise be accommodated by interactive execution.

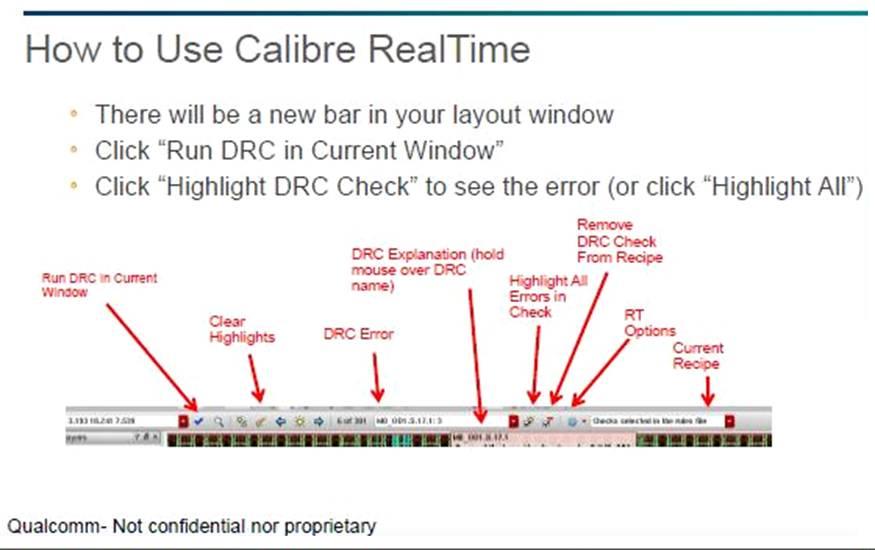

(4) iDRC tools are readily integrated into all layout platforms. As illustrated in the figure, toolbars and menus for iDRC are an integral part of the layout cockpit (as is the Calibre error report and viewing feedback). There is no need to exit from the interactive layout session, a big boost in productivity.

Tom W. is a big layout bindkey user — he has set up several bindkeys for common RealTime commands, as well.

(3) To be sure, iDRC does not replace batch verification. However, it is the most productive means to quickly verify the layout updates made to address batch run errors. The consistency of runsets used for both batch and interactive checking enables fast clean-up iterations using iDRC.

(2) Tom W. specifically highlighted that also iDRC enables a much quicker learning curve when starting layout design in a new process technology. The fast check, visualize, and fix loop helps the layout and circuit design team quickly explore initial cell/macro power rail and signal track template options.

The emphasis on a short learning ramp is consistent with a major theme of the 2015 TSMC OIP symposium. Early adoption and partnership with TSMC on advanced nodes is more important than ever, especially when making PPA design trade-offs.

and, finally, a very subjective advantage, but a critical one nonetheless:

(1)Every layout engineer wants to be as productive as possible. Schedule milestones are always tight, both during initial design feasibility assessment and the tapeout crunch. The morale (and stress) of the layout team is typically shared across the entire design team.

The enthusiasm that Tom W. displayed for iDRC with RealTime was infectious – you could tell the entire audience got a boost. Ensuring the design team can develop and maintain that high energy level throughout a project provides great benefits – this may seem somewhat intangible, but ultimately does affect the bottom line.

And, as an aside, if your team utilizes layout contractors for assistance with the (peak) workload, you want to be sure that word gets around this close-knit community that you’re making the investments to maximize layout productivity – you definitely want it to be known that you’re a great place to work!

If you haven’t looked at iDRC tools such as Calibre RealTime in a while, I would encourage you to do so – or, contact Tom W. and experience his ebullient recommendations directly. 🙂

-chipguy

Share this post via:

Comments

0 Replies to “Top 10 Reasons to invest in Interactive Design Rule Checking tools”

You must register or log in to view/post comments.