Intro

Earlier this month I drove to Mentor Graphics in Wilsonville, Oregon and spoke with Michael Buehler-Garcia, Director of Marketing and Nancy Nguyen, TME, both part of the Calibre Design to Silicon Division. I’m a big fan of correct-by-construction thinking in EDA tools and what they had to say immediately caught my attention.

Earlier this month I drove to Mentor Graphics in Wilsonville, Oregon and spoke with Michael Buehler-Garcia, Director of Marketing and Nancy Nguyen, TME, both part of the Calibre Design to Silicon Division. I’m a big fan of correct-by-construction thinking in EDA tools and what they had to say immediately caught my attention.

The Old Way

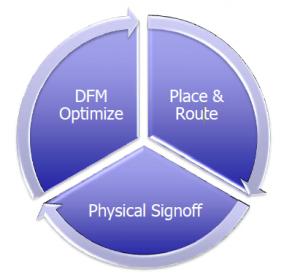

In a sequential thinking mode you could run a P&R tool, do physical signoff (DRC/LVS), optimize for DFM, find & fix timing or layout issues, then continue to iterate while hoping for manufacturing closure.

The New Way

Instead of a sequential process, what about a concurrent process? Well, in this case it really works to reduce the headaches of manufacturing closure.

The concept is that while the P&R tool is running it has real time access to DRC, LVS and DFM engines. This approach is what I term correct-by-construction and it creates a tight, concurrent sub-flow of tools to get the job done smarter than with sequential tools.

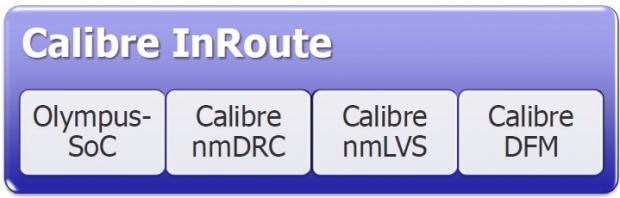

The product name is called Calibre InRoute and it includes the following four engines:

- P&R – Olympus SoC

- DRC – Calibre nmDRC

- LVS – Calibre nmLVS

- DFM – Calibre DFM

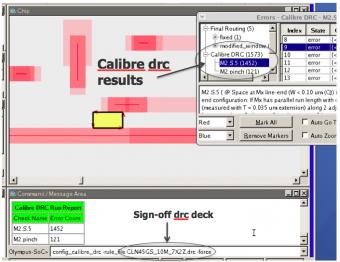

DRC Checking with the Sign-off Deck

Since Calibre is a golden tool for sign-off at the foundries it makes sense to use this engine and the sign-off rule deck while P&R is happening. Previous generations of P&R tools would have some rudimentary DRC checks embedded, but now that we have hundreds of rules at 28nm you cannot afford to rely on incomplete DRC checks during P&R.

What I saw in the demo was DRC checking results both in a text format and visual format. There was even a detailed description of what the DRC violation was.

OK, it’s nice to have DRC checking but what about fixing the DRC violations for me?

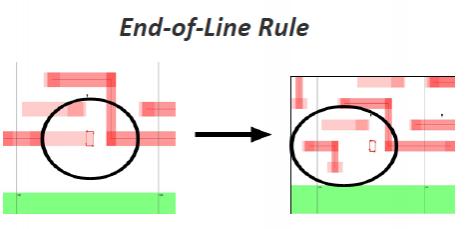

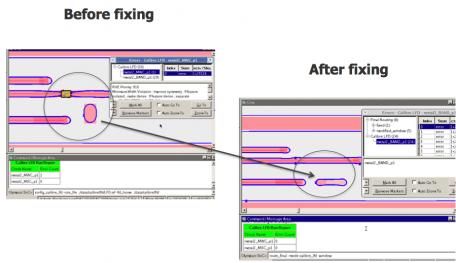

InRoute does just that. Here’s a DRC violation shown highlighted in Yellow:

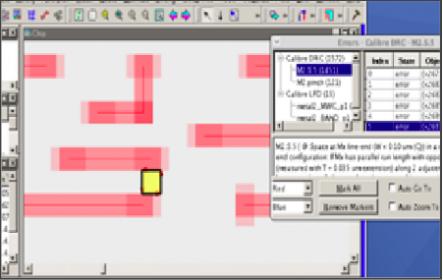

And the same area after the DRC violation has been automatically fixed for me:

DFM Issues – Find and Fix Automatically

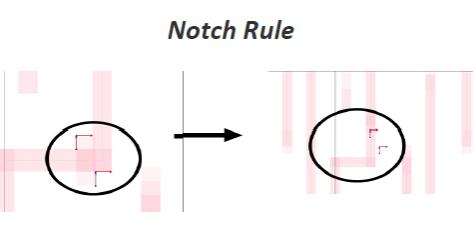

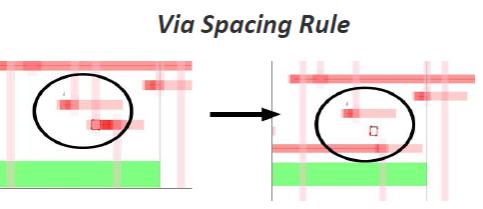

Just like DRC issues the InRoute tool can find and fix your DFM issues which saves time and speeds you through manufacturing closure more quickly:

Litho Friendly Design

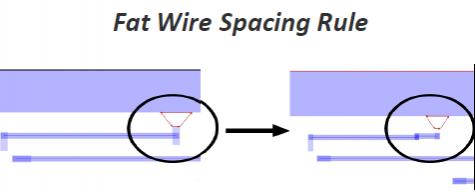

The perfectly rectangular polygons that we can draw in our IC layouts are not what ends up on the masks or silicon. The lithography process effects can be taken into account while InRoute is running to identify issues and even fix some of them. Here’s an example that shows a minimum width violation and how it was identified and auto-fixed:

Who is Using This?

STMicroelectronics is a tier-one IC design company that is one of the first to publicly talk about Calibre InRoute.

“We have used Calibre InRoute on a production 55nm SOC. InRoute has successfully corrected the DRC violations caused by several complex IPs, whose ‘abstract’ views did not fully match the underlying layout, as well as several detailed routing DRC violations,” said Philippe Magarshack, STMicroelectronics Technology R&D Group Vice President and Central CAD and Design Solutions General Manager.

Conclusion

It appears that the old ways of buying point tools (P&R, DRC, LVS, DFM, Litho) from multiple EDA vendors and creating your own sub-flows will get you through manufacturing closure with multiple iterations, while this new concurrent approach with EDA tools that are qualified by the foundries reduces iterations significantly. Calibre InRoute looks to be well-suited for the challenges of manufacturing closure by using a concurrent approach.

Comments

0 Replies to “DRC/DFM inside of Place and Route”

You must register or log in to view/post comments.