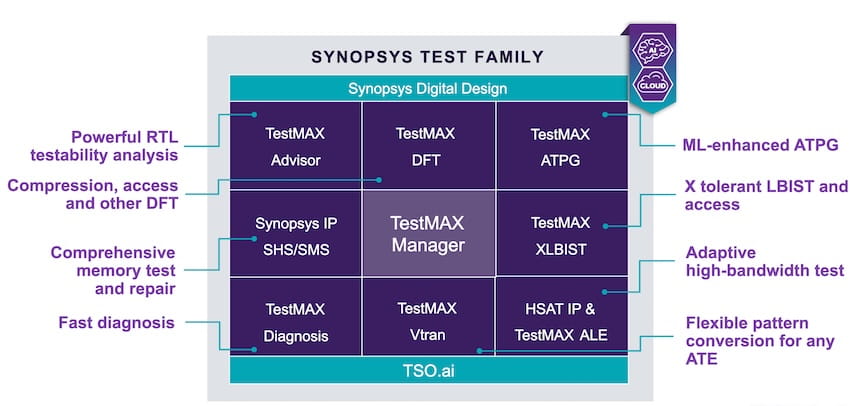

I first learned about ATPG – Automatic Test Program Generation in the 1980s at Silicon Compilers, then continued in the 90s at Viewlogic with the Sunrise tools, so it was illuminating to get an update from Synopsys on their ATPG technology by attending a webinar. Synopsys over the years has developed a family of test tools, shown below. Srikanth Venkat Raman, Product Management Director at Synopsys introduced how their ATPG has added features to become timing-aware, power-aware and use AI to minimize test cost.

Timing-Aware ATPG

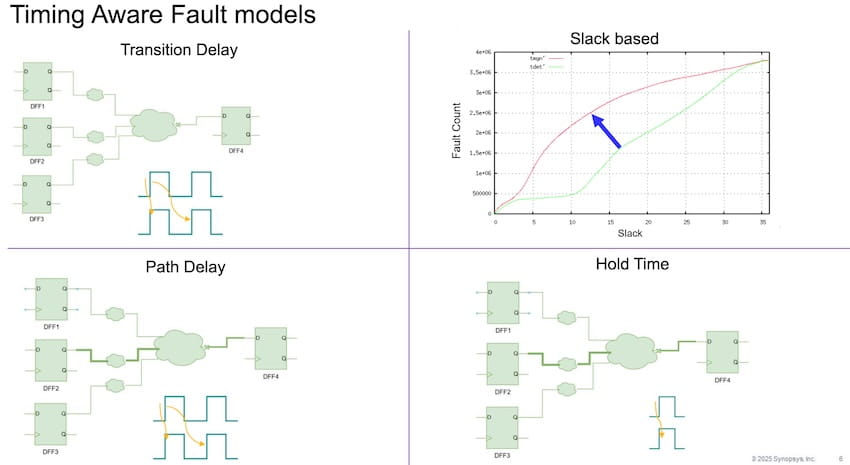

Bruce Xue, Staff Engineer described how timing-aware ATPG is made possible through fault models that account for: Transition Delays, Slack-based, Path Delay, Hold Time.

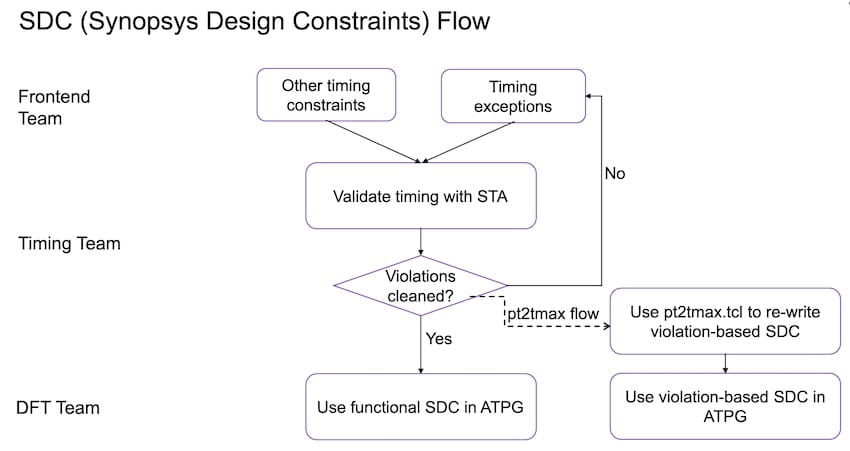

Using PrimeTime for Static Timing Analysis (STS) there are two ways to deal with timing violations, using functional SDC in ATPG or using violation-based SDC in ATPG.

Four challenges arise when using SDC in an ATPG flow:

- ATPG quality of results drop when using SDC

- Multi-cycle Path SDC is treated as False Path

- Violation SDC can’t match with the functional timing

- SDC written from PrimeTime has unnecessary commands for ATPG

New features in ATPG now address these challenges:

- Native SDC reading

- Multi-cycle Path ATPG

- Improved timing exception ATPG quality of results

- Write optimized SDC from PrimeTime

Five test results were presented showing improvements between 15% to 73% on total test cycle under the same test coverage using these SDC and MCP features. You get an improved SDC flow and QoR for better coverage and reliability.

Power-Aware ATPG

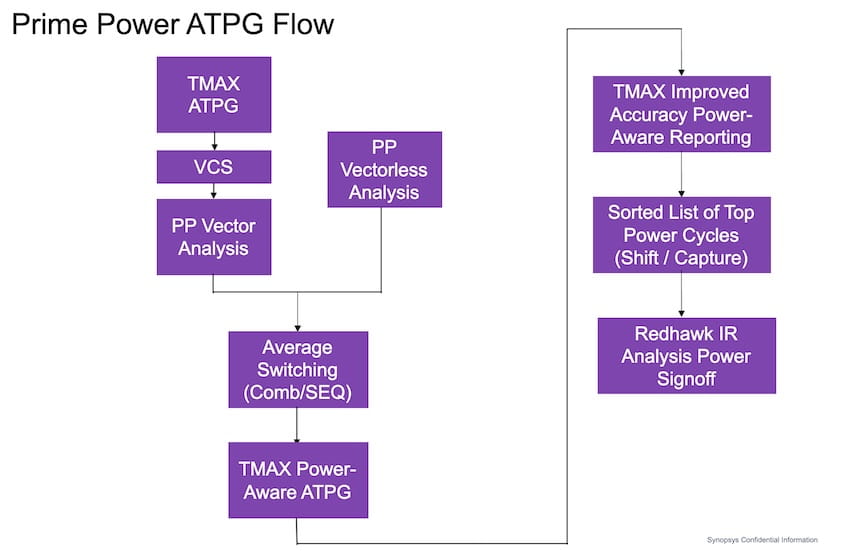

Khader Abdel-Hafez, Scientist, was up next on the topic of new power-aware ATPG features. The approach is to limit sequential cell switching to generate power-friendly ATPG patterns, use functional clock-gating switches, and during shift cycles to limit sequential cell switching. During ATPG test generation the power is estimated and the power results can be compared versus PriimePower, showing excellent correlation.

Tool users can set their power budget by limiting the number of scan cells and if some patterns exceed that budget, then those patterns are skipped. For power-aware shift support there’s a software-based approach to utilize adjacent fill to manager power during shift, or a hardware-based approach by turning off some chains during ATPG or using clock divider circuitry to limit switching during shift.

The PrimePower tool can also be used with the ATPG tool as shown in this flow diagram:

TestMAX ATPG has features to manager your chip power during both capture and shift operations, plus the integration with PrimePower improves power estimation during ATPG and improves QoR.

AI Technology

The final presenter was Theo Toulas, R&D Principal Engineer, and his topic was using AI technology called TSO.ai (Test Space Optimization) with TestMAX ATPG. TSO.ai aims to reduce your test times without changing tool flow while using the same CPU resources, and producing deterministic results.

Synopsys has AI embedded into TestMAX ATPG, so there’s no separate model maintenance and it learns from multiple designs run across an internal suite, so you just need to activate the feature in TestMAX ATPG. This AI technology analyzes your design from both simulation and design structure, applies learned strategies to optimize your ATPG parameters, then optimizes multiple ATPG heuristics using targeted solver efforts, producing a reduction in test cycles.

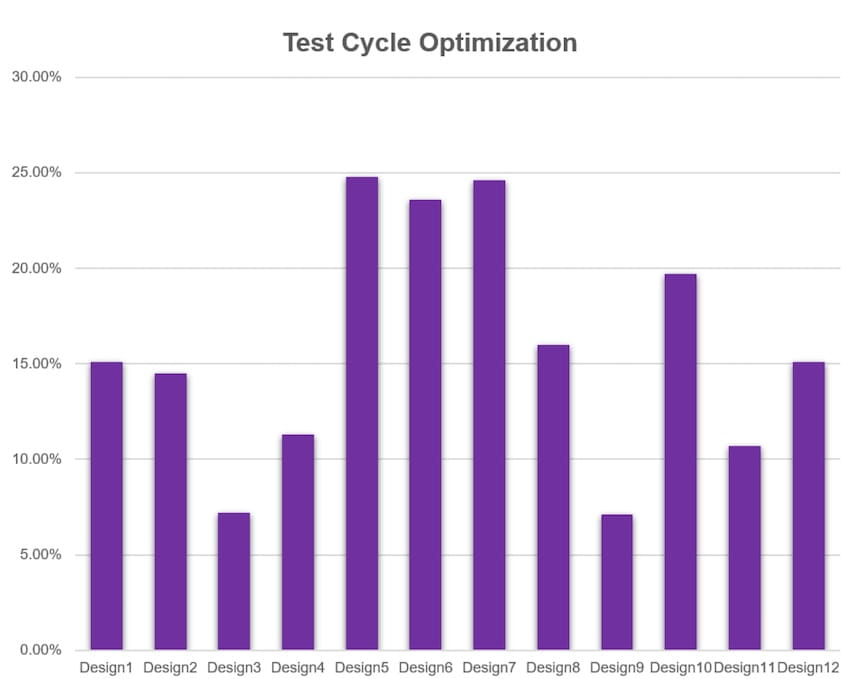

Feedback from customer designs show an average test cycle optimization of 15.81%, while increasing CPU runtime by 2.04X. Here’s a plot showing a dozen designs with test cycle optimization benefits:

Users just add a single command to the flow, turning on the ATPG learning feature, so there’s no learning curve involved.

Summary

Test engineers strive to meet fault coverage goals while staying within power budgets and trying to uncover any timing issues plus minimize test cycles. That’s a tall order to meet and manual methods are not sufficient for the task at hand. New ATPG features added by Synopsys are addressing these critical issues for test-aware and power-aware flows, while AI is helping optimize test cycles. Working smarter, not harder is what I saw in this webinar.

Watch the archived webinar after a brief registration online.

Related Blogs

- Statically Verifying RTL Connectivity with Synopsys

- Use Existing High Speed Interfaces for Silicon Test

- Addressing SoC Test Implementation Time and Costs

- Is Your RTL and Netlist Ready for DFT?

- Takeaways from SNUG 2023

Comments

There are no comments yet.

You must register or log in to view/post comments.