SoC projects are running behind schedule as design and verification complexity has increased dramatically, so just adding more engineers, more tests and more compute aren’t the answer. The time is ripe to consider smarter ways to improve verification efficiency. The added complexity of multiple embedded processors, multiple power domains, plus security and functional requirements create millions of corner cases. Brute-force verification methods no longer scale, so the team at Siemens have an approach with Questa One to unify coverage, changing verification from outdated methods into a targeted, intelligent, and collaborative discipline.

Coverage Plateau

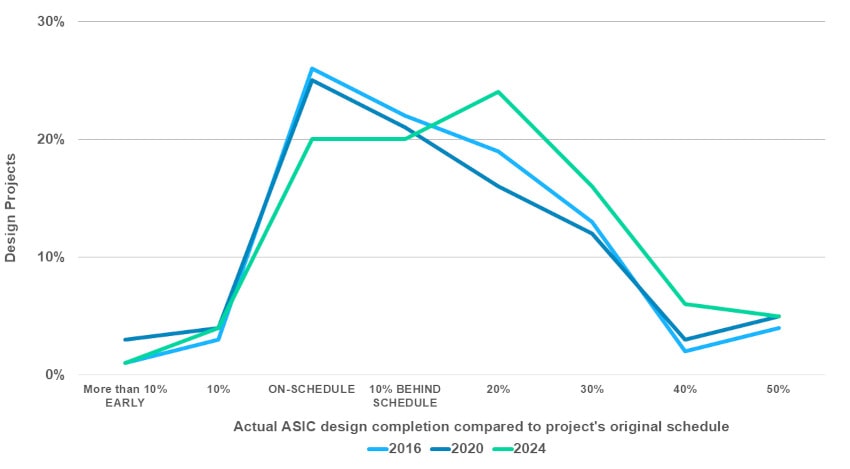

About 75% of complex ASIC projects are now missing schedule, up from 66% just a few years ago. Old verification methodologies typically stall at 85% coverage, no matter how many regressions you throw at it. Engineers are spending nearly half their time on verification activities, but with diminishing returns, huge regression suites and endless coverage reports. This coverage plateau has become a bottleneck, exposing the limits of traditional verification methodologies.

Intelligent Verification

Questa One has a new approach with a unified, end-to-end architecture that combines systematic verification planning, automated regression management, and real-time analytics. Instead of just launching more random tests, Questa One’s intelligence analyzes existing runs, identifies gaps, and generates targeted new tests. Coverage is pursued and directed strategically, breaking through old plateaus using fewer tests, and delivering project savings: coverage closure with 500x fewer tests, debug time cut by 30%, and regression times reduced by more than a third.

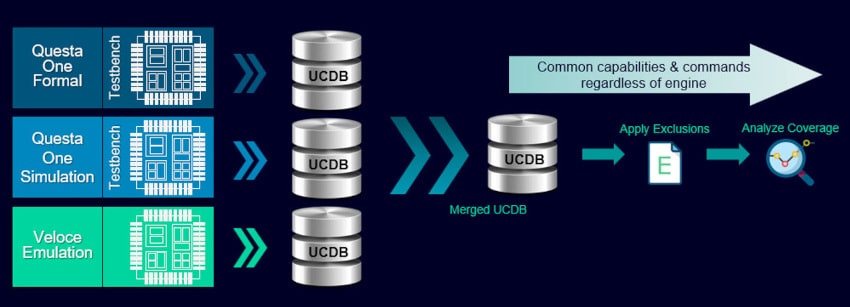

Unified Coverage Database

At the heart of this approach is a UCIS-compliant, unified coverage database (UCDB). This database bridges the entire verification journey, starting from the initial block-level analysis to simulation traces in a compute farm on the other side of the world. UCDB merges static, dynamic, code, functional, assertion, power, and safety coverage in one compressed format. Beyond just storage, this design enables collaborative features that reduce closure times by 20–25% and free up 100 engineering hours per week, all while maintaining continuity even as designs evolve.

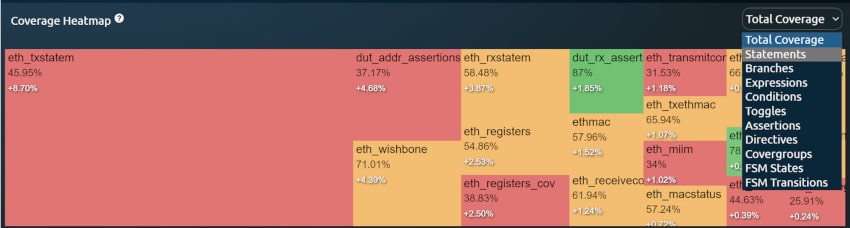

Questa One’s analytics use a browser-based dashboard with heatmaps to highlight where the next 10% of coverage can be won. Machine learning algorithms find and rank test effectiveness, suggest regression optimizations, and provide historical trend visualizations. Pattern matching groups related coverage issues, saving verification engineers from manual deep-dives into the tiniest test disruptions.

Coverage Acceleration and Debug

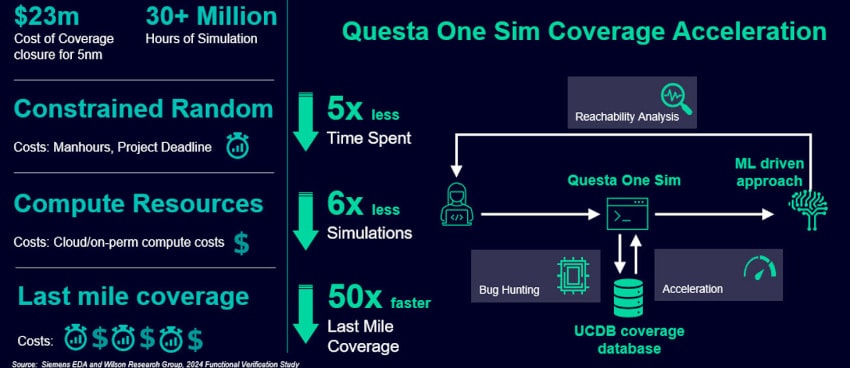

To improve coverage from 80% towards 100% requires something new. Traditional approaches require teams to just run more tests, but Questa One Sim Coverage Acceleration (QCX) takes a smarter approach. QCX analyzes the coverage landscape, maps the most efficient routes, and generates only the tests required to reach closure. Where a large SoC regression might have taken a week, it now closes in under an hour with QCX. Peripheral IPs that once took thousands of test cases can now be fully verified with a couple hundred. QCX’s guided approach achieves 100% coverage where brute force fell short. The result is up to 100x faster time to closure, a big help for teams under pressure to meet their schedule.

Coverage Acceleration and Debug

To improve coverage from 80% towards 100% requires something new. Traditional approaches require teams to just run more tests, but Questa One Sim Coverage Acceleration (QCX) takes a smarter approach. QCX analyzes the coverage landscape, maps the most efficient routes, and generates only the tests required to reach closure. Where a large SoC regression might have taken a week, it now closes in under an hour with QCX. Peripheral IPs that once took thousands of test cases can now be fully verified with a couple hundred. QCX’s guided approach achieves 100% coverage where brute force fell short. The result is up to 100x faster time to closure, a big help for teams under pressure to meet their schedule.

Summary

Questa One has many unified pieces: planning, verification engines, closure, dynamic debug, analysis, regression and process management. Used together these pieces create an environment that’s always adapting, always optimizing. Each tool amplifies the effectiveness of the others, turning verification into a coherent, nimble, and ultimately more efficient process.

Read the entire 28 page white paper online.

Related Blogs

- CDC Verification for Safety-Critical Designs – What You Need to Know

- Smart Verification for Complex UCIe Multi-Die Architectures

- Siemens EDA and Nvidia: Pioneering AI-Driven Chip Design

- Siemens Proposes Unified Static and Formal Verification with AI

- Revolutionizing Simulation Turnaround: How Siemens’ SmartCompile Transforms SoC Verification

- The Siemens Questa plus AI Story Gathers Momentum

Comments

There are no comments yet.

You must register or log in to view/post comments.