By Kamal Khan

In today’s semiconductor industry, success hinges not only on innovation but also on discipline in managing complexity. Every system-on-chip (SoC) is built from hundreds of reusable IP blocks—standard cells, memories, interfaces, and analog components. These IPs are the foundation of the design. But if the foundation is weak, even the most ambitious architecture can fail.

This is where IP Quality and Governance in IPLM (Intellectual Property Lifecycle Management) become critical. They are not “nice to have” features. They are guardrails that protect design teams from costly errors, late rework, and unpredictable tape-outs.

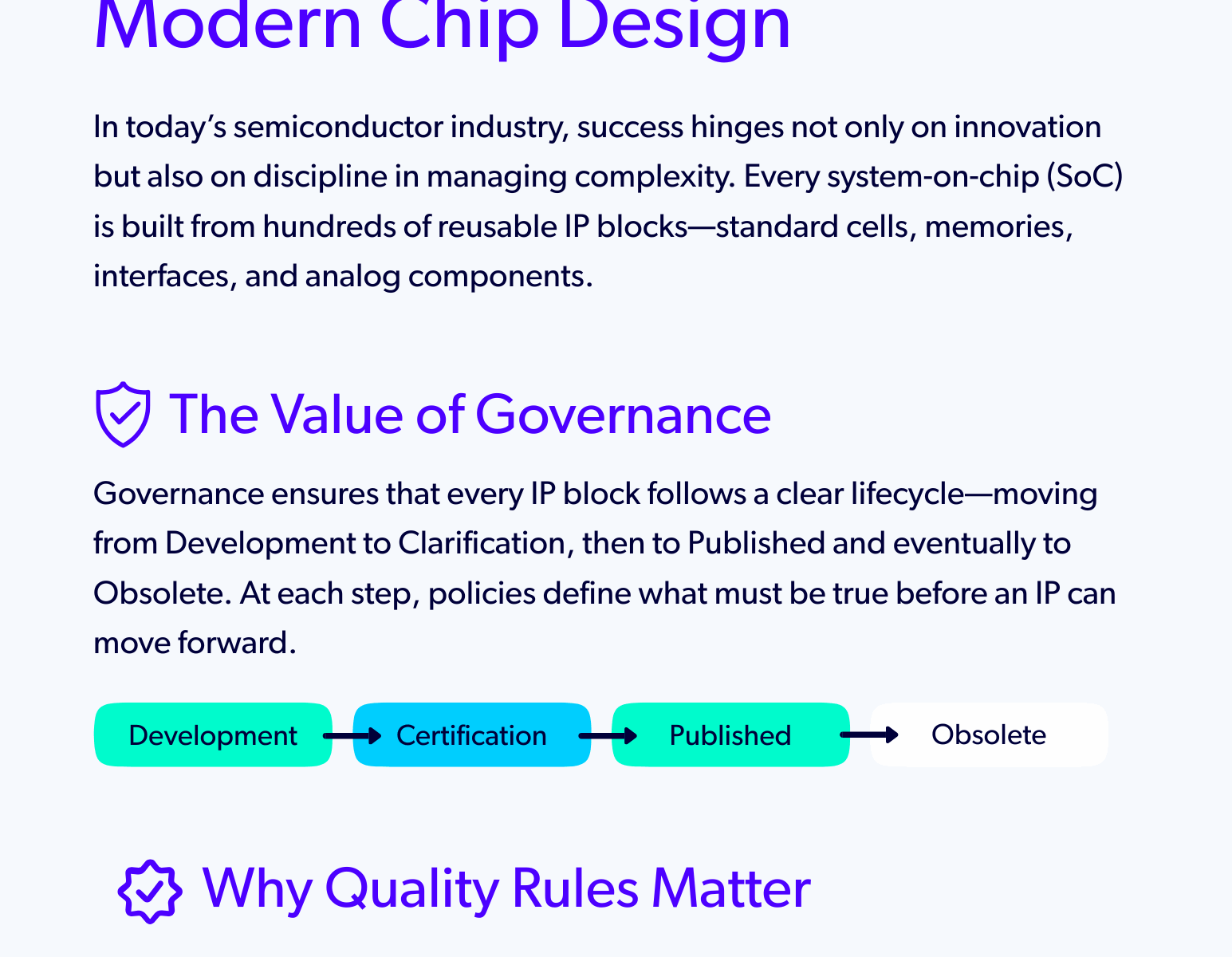

The Value of IP Governance

Governance ensures that every IP block follows a clear lifecycle—moving from Development to Certification, then to Published, and eventually to Obsolete. At each step, policies define what must be true before an IP can move forward.

This isn’t about bureaucracy—it’s about consistency and trust. In a world where design teams are distributed across continents, governance makes sure that everyone is working from the same playbook.

Why Quality Rules Matter

IP Quality checks are the quality gates that enforce readiness. Instead of relying on subjective judgment, they apply automated rules and checklists:

- Does this IP version pass all regression tests?

- Is the CAD environment aligned with the correct process node?

- Are mandatory properties and metadata captured?

- Has it cleared security or licensing requirements?

The answer is binary: Pass or Fail. Only when an IP meets the defined criteria does it advance.

This objectivity reduces risk, improves confidence, and accelerates integration.

Real-World Examples

1. Safeguarding Tape-Out

A global SoC team nearly missed a major smartphone launch because a third-party IP was integrated at the wrong maturity level. The bug was caught late and fixing it cost both schedule and reputation. With IPLM governance, only Final-certified IPs would have been allowed into the design at tape-out, preventing the slip.

2. Ensuring Process Compatibility

An analog IP provider released an updated block for a 5nm process. Governance rules automatically checked the metal stack property. The rule flagged a mismatch before integration, saving weeks of debug time.

3. Enabling Global Collaboration

A memory IP updated in the U.S. was inadvertently used by an Asia-based team before it was production-ready. With IPLM, policies enforce semantic versioning and access control, ensuring that immature IPs stay restricted until they’re validated.

The Bigger Picture

The cost of a re-spin can run into the tens of millions. The cost of late discovery can be even higher: lost market windows.

By embedding IP Quality and Governance into the design process, organizations gain:

- Predictability: Designs progress with fewer surprises.

- Traceability: Every decision, rule, and approval is logged.

- Scalability: Teams across geographies work with the same trusted data.

Closing Thought

In an era where semiconductor complexity grows faster than design cycles, discipline is the new differentiator. IP Quality and Governance in IPLM aren’t just technical features—they are strategic enablers of faster, safer, and smarter innovation.

Kamal Khan is Perforce Vice President North America Automotive/Semiconductor. He has over 20 years of domestic and international experience, specializing in PLM, Data Management, IP lifecycle management, IoT Security, Semiconductors, Enterprise software, EDA, CAD, 3D Printing, Cloud solutions.

This article was originally published on Perforce.com. For more information on how Perforce IPLM streamlines semiconductor development , visit https://www.perforce.com/

Also Read:

IPLM Today and Tomorrow from Perforce

Perforce and Siemens at #62DAC

Perforce Webinar: Can You Trust GenAI for Your Next Chip Design?

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.