You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

By Kamal Khan

In today’s semiconductor industry, success hinges not only on innovation but also on discipline in managing complexity. Every system-on-chip (SoC) is built from hundreds of reusable IP blocks—standard cells, memories, interfaces, and analog components. These IPs are the foundation of the design. But if the foundation… Read More

For those who design advanced and complex SoCs, the term “off-the-shelf IP” can be elusive. While this approach works for a wide range of IP titles, the pressure for maximum performance or minimum power can lead to custom-tailoring requirements for the IP.

PLDA has seen these requirements for the class of complex, high-performance… Read More

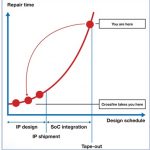

IP must be properly qualified before attempting to use them in any IC design flow. One cannot wait to catch issues further down the chip design cycle. Waiting for issues to appear during design verification poses extremely high risks, including schedule slippage. For example, connection errors in transistor bulk terminals where… Read More

In the history of semiconductor design and manufacturing, the age-old concept of DRC rule-deck qualification for handshake between design and manufacturing still applies strongly to produce working silicon. In fact, DRC clean GDSII works as the de facto golden gate between a design and a foundry for manufacturing the chip for… Read More

In an SoC world driven by IP, where an SoC can have hundreds of IP (sourced not only from 3[SUP]rd[/SUP] party but also from internal business units which can have a lot of legacy) integrated together, it has become essential to have a comprehensive and standard method to verify and signoff the IP. Additionally, these checks must … Read More

As SoC design has transformed from being about writing RTL and more towards IP assembly, the issue of IP quality has become increasingly important. In 2011 TSMC and Atrenta launched the soft IP qualification program. Since then, 13 partners have joined the program.

IP quality is multi-faceted but at the most basic level, an IP block… Read More

Atrenta is having a special offer to let you “spring clean” your IP for free. They are providing two weeks of free access to the Atrenta IP kit starting from today, April 16th, until the end of May. During this period, qualified design groups in the US will be able to use the kit for two consecutive weeks to “spring… Read More

Now that the dominant approach to building an SoC is to get IP from a number of sources and assemble it into a chip, the issue of IP quality is more and more critical. A chip won’t work if the IP doesn’t work, but it is quite difficult to verify this because the SoC design team is not intimately familiar with the IP blocks since… Read More

Atrenta has four seminars coming up on SoC realization. More and more design is actually about finding IP and integrating it together at the block level, and then handing it off to a standard RTL to GDSII flow. The three focus areas are:

- finding quality IP faster

- accelerating IP integration and SoC assembly

- handing off RTL successfully.

…

Read More