Calibre is a well-known EDA tool from Siemens that is used for physical verification, but I didn’t really know how AI technology was being used, so I attended a Tuesday session at #62DAC to get up to speed. Priyank Jain, Calibre Product Management presented slides and finished up with a Q&A session.

In the semiconductor world we’ve seen a hardware-centric viewpoint starting with PCs in the 80s and 90s, where software ran on general-purpose hardware. Today, it’s more of a software-defined world, where the software architecture drives the hardware implementation.

The vision with Calibre is to shift-left and reduce Turn Around Time (TAT), accomplished by running the tools earlier in the design and implementation flows and using AI techniques. A huge challenge of trying to run full-chip integration earlier is that it produces billions of DRC errors, making the tool load slowly, increases debug time, all with little collaboration between engineering team members on what to fix first.

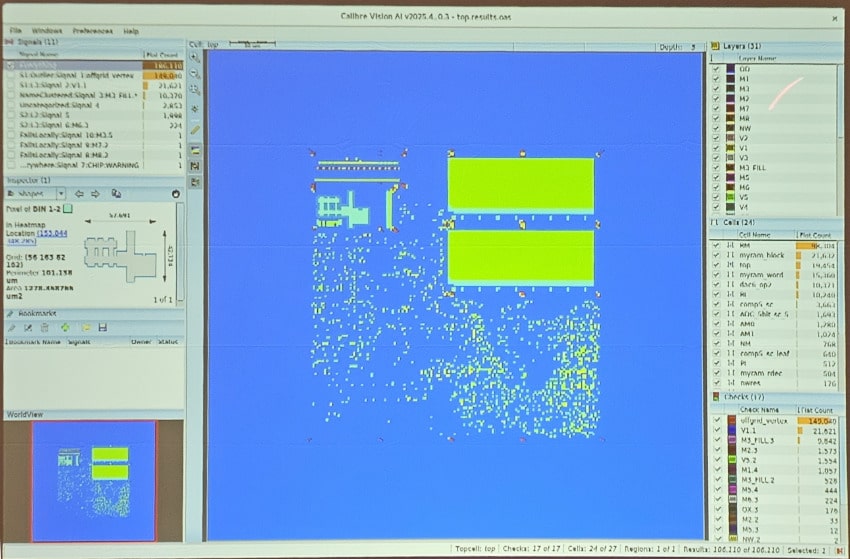

This challenge led to a new product called Calibre Vision AI, which enables full-chip analysis earlier in the implementation process by adding intelligent debug and user collaboration. With this new tool, engineers can quickly make sense of a DRC run that has billions of errors, as the AI feature clusters similar errors together making it easier to identify systematic issues such as block overlap, bad via, fill overlap and more, and let’s you prioritize which errors should be fixed first.

Calibre Vision AI has a modern, multi-threaded foundation for fast operation. A GUI with dynamic panels for quick debug, and navigation features to pinpoint the source of errors.

The GUI helps visualize a heat map, showing the density of DRC errors. AI is used to cluster similar errors, and the AI works across all IC layout technologies with no model training required for tool users. Common failure causes are easily identified so that you will be more productive in fixing DRC errors. As an engineer uses the tool they can use dynamic bookmarks on the layout to capture, assign work and write notes for other team members to collaborate on the fixes.

It’s recommended that you run the Calibre RVE tool at the block level and for tapeouts, and run Calibre Vision AI for chip-level analysis at early stages, as the two tools complement each other. Using Calibre Vision AI for full-chip analysis accelerates full-chip debug through the high capacity and multi-threaded technology. Heat maps of errors show the entire die, so that you can pinpoint areas of highest interest. Results are visualized instantly, even when its millions of errors. One comparison showed that for 790 million DRC errors a traditional ASCII flow would load in 15 minutes, while a Vision AI flow using OASIS loaded in just 45 seconds.

Early users of Vision AI reported that it was faster to identify systematic issues and that DRC debug iterations were cut in half. For example, one run had 600M errors from 3,400 checks, then that was reduced to just 381 signal groups or clusters.

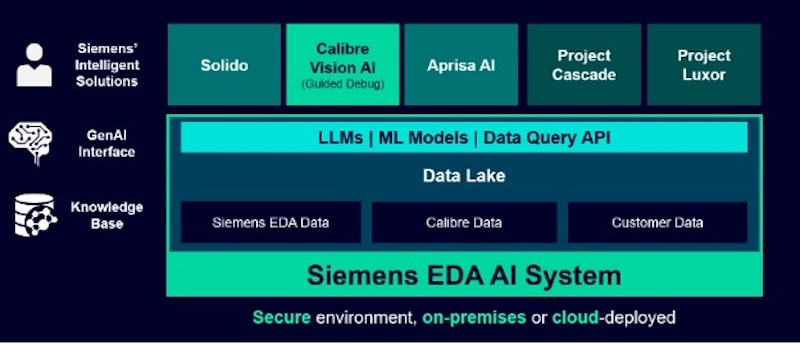

Siemens has many EDA tools using AI techniques.

There are three places where AI is used in Calibre Vision AI:

- Chatbot – EDA knowledge using prompts

- Reasoning – Data analysis and summarization

- Tool Operations – Performing complex tool functions from prompts

Summary

DRC analysis and debug work can now reduce tasks that required hours into just minutes by using AI-based clusters. Teams doing physical design can collaborate and communicate more efficiently by using bookmarks, block debug and attaching reports.

Q&A

Q: Is there any plan to Auto-fix DRC errors?

AI quickly groups similar DRC violations for easier root-cause analysis, but we still need a human in the loop to fix the violations.

Q: Can I create new Signals?

A: Vision AI comes with a set of Signals out of the box, and I can also create their custom signals by my own checks (i.e. M1 checks first).

Q: What’s the difference between RVE classifier and AI?

A: AI takes and elevates the classifier by 100X, analyzing the results, locations, proximity, root causes, cluster by groups. RVE is good for fewer errors, but AI works on billions of errors and earlier in the process.

Q: Can you aggregate AI across multiple designs, trends, library cells in common, broad trends?

A: It’s under development, stay tuned for a future release.

Q: Are signal groups an AI classification?

A: We use unsupervised learning to create the groups by location, proximity.

Related Blogs

- Siemens EDA Unveils Groundbreaking Tools to Simplify 3D IC Design and Analysis

- DAC News – A New Era of Electronic Design Begins with Siemens EDA AI

- Siemens EDA Outlines Strategic Direction for an AI-Powered, Software-Defined, Silicon-Enabled Future

- Going Beyond DRC Clean with Calibre DE

- Speeding Up Physical Design Verification for AMS Designs

- Getting Faster DRC Results with a New Approach

Comments

There are no comments yet.

You must register or log in to view/post comments.