The number of touchpoints between analog and digital circuits in high performance SoCs is increasing. This is not a problem because it is possible to implement critical analog blocks directly on nanometer scale digital ICs. However, in many cases digital interfaces or digital feedback circuitry configures these analog blocks to improve their performance. As a result, not only do the interfaces between these blocks need to be functionally correct, they need to perform properly when subjected to stresses and strains that are endemic to analog circuits. With more interactions between digital and analog blocks there comes a greater need to verify the entire design with mixed signal simulation for proper behavior in many scenarios and over lengthy time intervals.

Mentor, a Siemens business, has written a white paper on the topic of high performance and high accuracy mixed signal simulation. The paper is titled “Expanding the Scope of Mixed-Signal Verification With Symphony Mixed-Signal Platform”. It talks about verifying the many sensitive analog blocks used in SoC designs, such as PLLs, SerDes, data converters, high voltage switches, high frequency oversampling DACs, charge pumps, and more. These blocks are subject to noise, and variations in process, temperature and voltage.

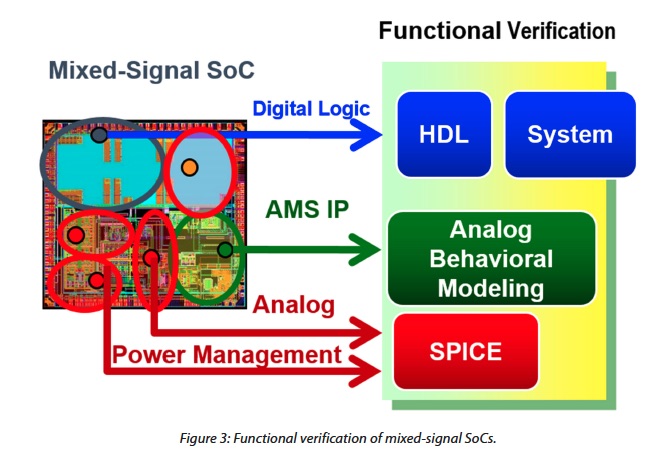

Mixed signal simulation offers a way to run at different levels of abstractions to provide a tradeoff between runtime and accuracy. This gives designers quicker ways to check for functional issues such as errors or conflicts in integration of the mixed signal blocks at their interfaces. But the Mentor paper points out that this is only part of the battle. Full verification requires complete analysis of analog behavior over a wide range of operating conditions.

Realistic Analog Behavior

High accuracy SPICE simulation is needed to look at what the paper calls realistic analog behavior, often with repeated runs to account for variation, etc. As you are already aware, Mentor has been assembling quite an impressive suite of analog simulation tools over the years. In 2014 they acquired Berkeley Design Automation which provided the technology for their Analog FastSPICE (AFS). Their acquisition of Solido added advanced Monte Carlo and variation simulation tools. Additionally, Mentor offers advanced digital simulation with Questa. However, by themselves these are not enough to tackle the mixed signal simulation challenges of today.

Combined Simulation

The paper focuses on how Mentor’s Symphony mixed signal simulation platform brings together all these strong simulators and ones from other vendors, as well, to solve the difficult challenges faced by SoC designers. Integration with AFS means that large analog circuits can be accurately simulated to reveal realistic analog behavior. Digital blocks can be described in Verilog, SystemVerilog, or VHDL and analog blocks can be described at the transistor level in SPICE or Verilog-A.

The real secret sauce in Symphony is the A/D Boundary Element (BE). They come already coded and users can easily configure them through parameters. Users can configure the built-in BEs for each specific instance. There are even supply sensitive BEs that can model behavior as the power rails rise to full power.

Real World Cases

The white paper cites two examples where Symphony can help verify complex circuit operation. The first case is pipeline ADCs, where there are feedback loops that are normally very difficult to verify. In particular they discuss the case where there can be either a dual or single supply. Designers need to tune power on reset circuits so they function properly in either case. The second example they offer involves verifying the auto calibration inside a memory controller. Auto calibration is essential for proper synchronization of the data signal and the corresponding strobe.

Conclusion

The paper makes good reading with regard to these two examples, and the larger issue of how important mixed signal simulation is to the verification of high performance SoCs. The flexibility, usability and performance of Symphony make it a key element in SoC design flows. The full white paper is available for reading through the Mentor website.

Share this post via:

Comments

One Reply to “White Paper – Mixed Signal Verification for Nanometer SOCs”

You must register or log in to view/post comments.