Tom Fitzpatrick, a Strategic Verification Architect at Mentor, a Siemens Business, has worked on IEEE and Accellera standards like Verilog 1364, System Verilog 1800, UVM 1800.2 and is Vice Chair of the Portable Stimulus working group, so when I heard that he was doing a webinar on how PSS can be used to create better stimulus for a UVM environment, I previewed it right away to improve my understanding. The webinar helped me better understand the important and powerful relationship between PSS and UVM and also included a few details about how Mentor is making PSS technology available “under the covers” for UVM users in their inFact CX product. For those interested, the webinar will be hosted on Tuesday, May 26th from 10am-11am PDT and you can register here. I’ve included what I believe to be some stand-out points below.

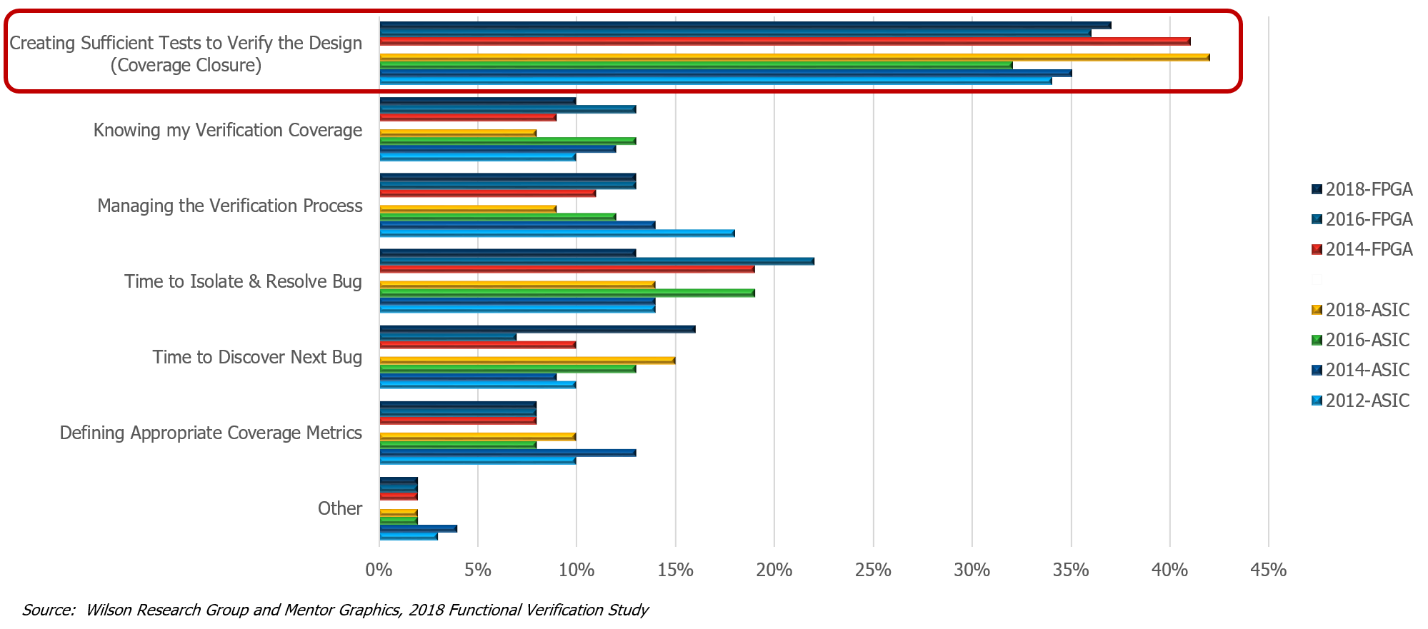

A biannual verification survey conducted by Wilson Research Group has listed the biggest verification challenge for both ASIC and FPGA users as the ability to create sufficient tests to verify the design and achieve coverage closure.

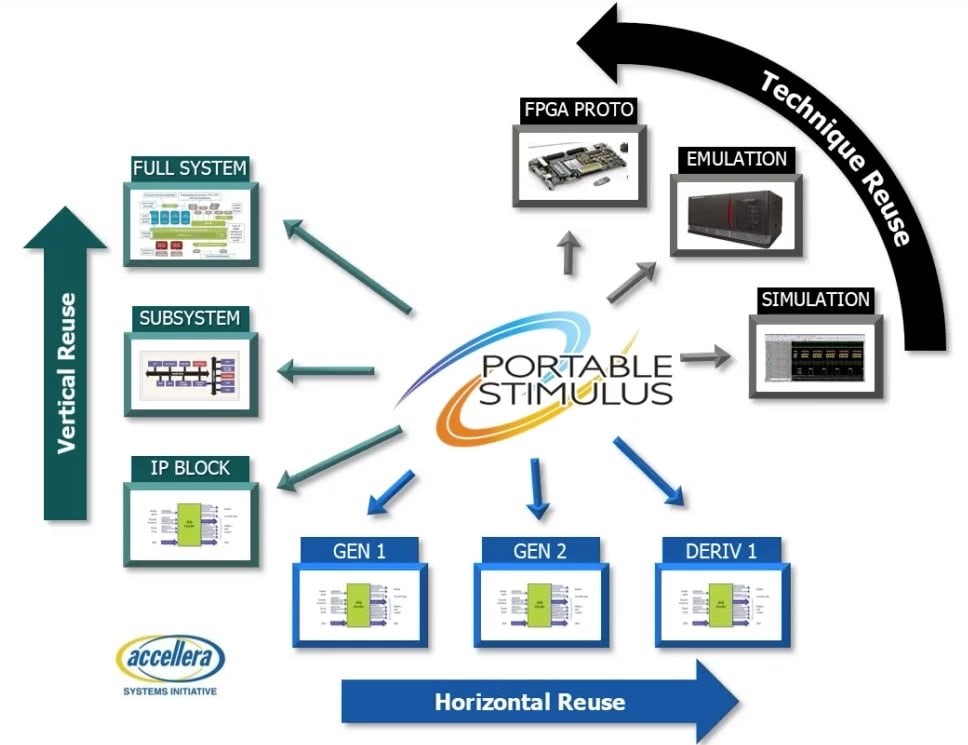

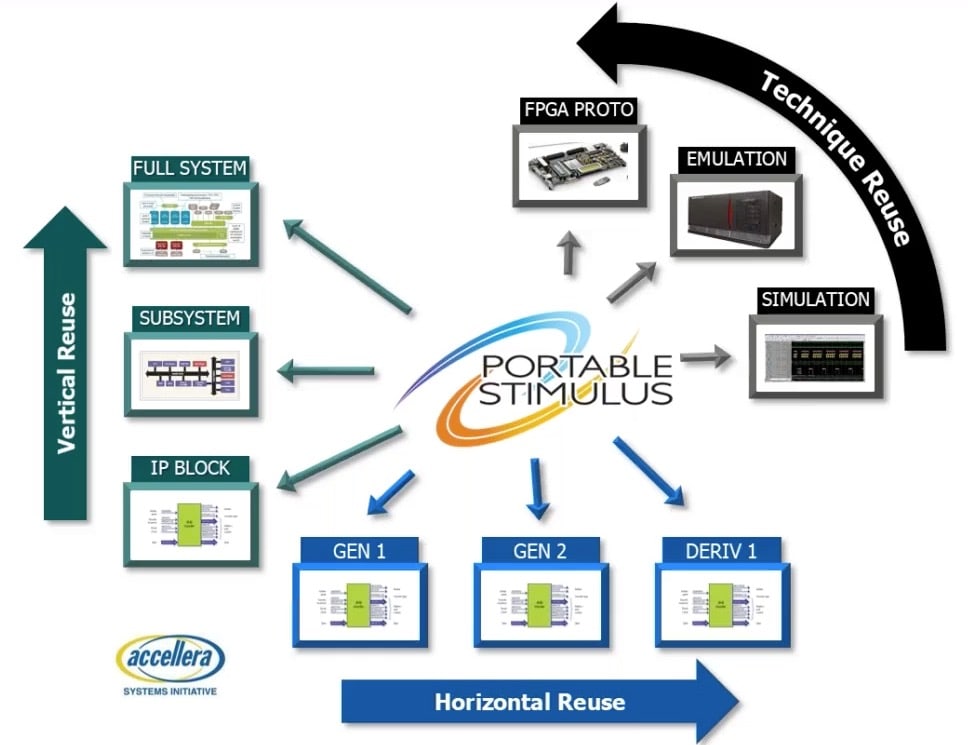

The Portable Test and Stimulus Standard (PSS) provides a common verification language across IP blocks, subsystem and full system. Even as your SoC goes through multiple generations, you can reuse verification intent. Finally, you can use a single specification across simulation, emulation and FPGA prototyping, saving you much time as compared to separate approaches.

In the specification of PSS it states, “The goal is to allow stimulus and tests, including coverage and results checking, to be specified at a high level of abstraction, suitable for tools to interpret and create scenarios and generate implementation in a variety of languages and tool environments, with consistent behavior across multiple implementations.”

So, UVM is just one possible target environment for Portable Stimulus.

A typical UVM verification flow starts with a sequence item and set of constraints, then it’s run through random simulation, sending transactions through the agent to the DUT, covergroups measure coverage metrics, but then we often realize that our coverage goals are not met. At this point, we can write new constraints to target additional coverage, but ultimately we need to write directed tests to reach the last 5-10% of coverage.

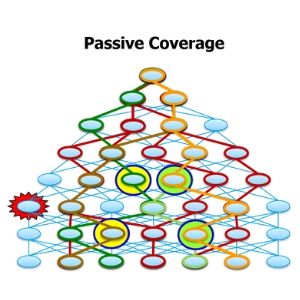

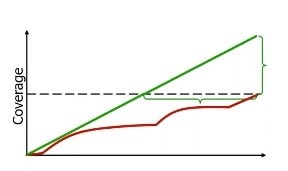

This is the result of constrained-random simulation treating the coverage specification as passive. In a typical constrained-random testbench, you are defining your critical states (green circles), and then constrained random tests hit those states in unpredictable ways. On the downside, constrained random will often repeat states or entirely miss coverage points. With this passive coverage approach we can still see lots of uncovered states, including states that may indicate a bug.

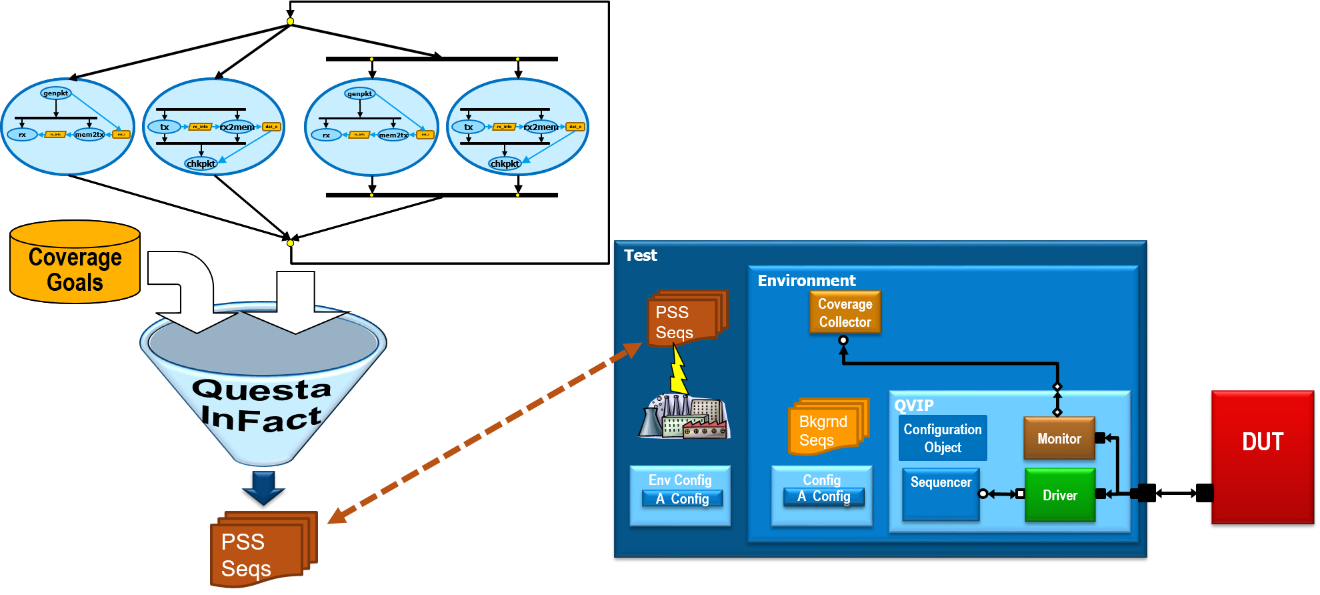

Instead of relying on procedural tests and hoping you’ll hit your coverage goals, PSS is a declarative language that lets you define scenarios at an abstract level and lets your tool, such as Questa inFact, generate different target-specific implementations of the abstract scenarios in either SystemVerilog (including UVM) or C. Because the PSS scenarios are fully declarative, the tools can analyze the scenarios and generate tests that actively target your coverage goals.

Thus, a tool like Questa inFact can generate the minimum number of tests required to reach your coverage, and then generate all other legal scenarios that will fully exercise all other states, including the one with the bug.

When all is said and done, the PSS description is transformed into a UVM virtual sequence that calls lower-level UVM sequences in the right order to implement the abstract scenario you described.

You can then use the UVM factory to simply swap in the PSS-generated sequences into your existing UVM environment without having to change any of your UVM code.

Summary

PSS allows you to look at verification from a higher level, because it’s declarative. This does require a change in thinking for most UVM users. Mentor’s Questa inFact automates a lot of the analysis to hide most of the PSS details and extracts the important details from your existing UVM code to build a coverage-targeted test for you. As you can see below, using PSS with a tool like Questa inFact (green line) when compared to constrained-random (red), lets you reach your test coverage goals much more efficiently, giving you more time to explore additional scenarios outside of your coverage scope, with the promise of 2-3X improvement in regression efficiency.

Plan to signup and attend this webinar online on May 26th, which also includes a Q&A.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.