Hierarchy is nearly universally used in the SoC design process to help manage complexity. Dealing with flat logical or physical designs proved unworkable decades ago. However, there were a few places in the flow where flat tools continued to be used. Mentor lead the pack in the years around 1999 in helping the industry move from flat DRC to their Calibre hierarchical DRC flow. Similarly, now Mentor is on the leading edge of the move to hierarchical Design for Test (DFT), a part of the flow that has for many years resisted switching from a predominantly flat approach.

Mentor has a white paper that does an excellent job of highlighting the numerous advantages of taking a hierarchical approach for DFT. The white paper, titled “Hierarchical DFT: Proven Divide-and-conquer Solution Accelerates DFT Implementation and Reduces Test Costs”, also explains how the flow works and how many of the benefits are achieved. The author, Jay Jahangiri, specifically dives into the key features of Mentor’s Tessent Hierarchical DFT solution that are used in a hierarchical flow.

Looking at the advantages of hierarchical DFT, you could guess the top handful of motivations for using it. These include shortened DFT implementation and ATPG runtimes. Another would be eliminating the large memory footprint for loading designs for implementation or analysis. Often these operations take hundreds of gigabytes of memory, severely limiting the number of available machines that can be used for these jobs.

Some of the other reasons for switching to a hierarchical approach are pretty compelling too. For instance, running flat test patterns can consume a lot of power and create hot spots. Hierarchical approaches can reduce power, and help manage and avoid hot spots more easily. It is also worth reflecting on how DFT is often in the critical path for tape out. The reduction in time required for hierarchical DFT and the reduced turnaround time for changes it provides can make a crucial difference in the time needed overall for DFT, especially at the end of the process. The Mentor white paper is quite thorough in enumerating the reasons for switching to a hierarchical approach.

Of course, if working hierarchically was easy this approach would have been used to solve the problem from the outset. It turns out that a number of key elements are needed to make it work effectively. In their white paper, Mentor provides an easy to follow summary of these elements.

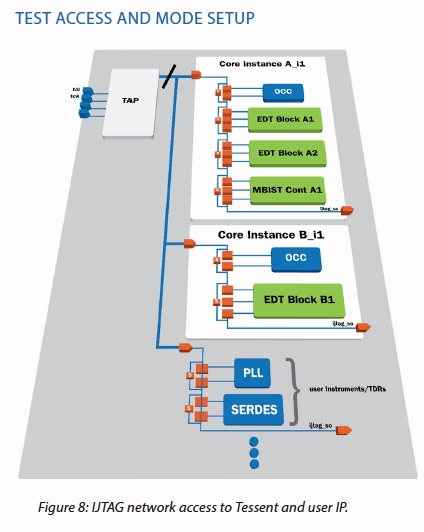

Because clocking plays such an important role in DFT, Mentor makes it easy to insert on-chip clock controllers (OCCs) into blocks so that each block can run its test patterns independently of other blocks’ test clock needs. Removing the interdependencies caused by top level clocking leads to a dramatic improvement in efficiency.

Tessent’s Scan and ScanPro products not only help with adding wrapper cells to create wrapper chains, they also allow analysis and utilization of existing registers for use during test as a shared wrapper cell. They also discuss several aspects of handing internal mode and external mode, to fully cover not just blocks but the glue logic between them.

The real enabler for making a hierarchical flow work is how smoothly the flow works. There are many aspects involved in not only making the blocks themselves testable, but also in integrating each block’s test elements into the top-level design. Tessent uses enabling technology, such as IEEE 1687, also known as IJTAG. Tessent also lets designers perform a lot of the test design at RTL, saving time and reducing complexity.

With performance gains in some steps of the process of up to 5 or 10X, the hierarchical approach is proving to be an effective way to deal with test complexity. It brings with it many interesting advantages as well that it can improve yield analysis and overall chip quality. The white paper goes into much more detail on exactly where the gains are and how the process improves productivity and quality. The paper can be downloaded from the Mentor website.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.