The server market has been undergoing changes in the last few years. The traditional go-to for server processors had been x86 based chips from Intel or AMD. However, if you go on Amazon AWS looking for EC2 instances, you will see the “A1” instance type, which is an ARM based instance. This is not what you might think at first. The A1 instance uses AWS Graviton processors which are based on 64-bit ARM Neoverse cores and custom silicon designed by AWS. Amazon is not the only company building servers using the Neoverse cores.

With ARM’s CMN-600 mesh interconnect, up to 128 or more cores can be connected in hyperscale servers for impressive processing power combined with high throughput and power efficiency. There is already a wide ecosystem of OSs, development tools and application software available for Neoverse based machines. These include several flavors of Linux, VMWare, Docker, and all the usual software stacks for web and internet-based services.

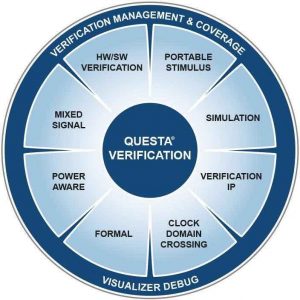

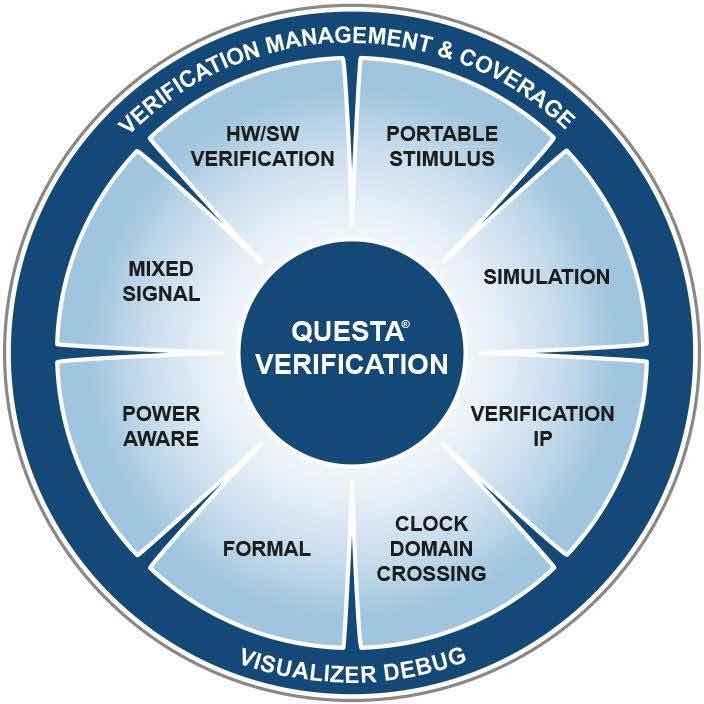

Where it gets interesting for chip designers, however, is that computationally intense design tools are now available for this platform as well. Mentor has just announced that their Questa verification suite is available on the 64-bit Neoverse processors. Mentor decided to do this based on their assessment of market demand. Of course, ARM, a large user of verification tools, wanted this, but also Mentor found that other customers wanted this new platform. And, of course if the Neoverse machines are not in-house, running jobs on AWS is a readily available option.

Questa already is OS agnostic, running interchangeably on Windows or Linux. The ability to run on x86 or Neoverse machines gives their customer more choices. Mentor has made the selection of processor architecture easy to do at runtime. The implementations are bit for bit compatible, so the same results will be achieved regardless of the platform. Mentor partnered with ARM on development and qualification. Already Mentor has announced qualification of a number of server manufacturers that are producing Neoverse based servers.

Prior to this announcement I had a conversation with Neil Hand, ICVS Director of Marketing at Mentor to talk about their new support for the ARM Neoverse cores. He highlighted the power, performance and price benefits of running on the new ARM based servers. Another key advantage in his mind is the very high memory bandwidth they offer. Digging into the details, he said the porting process was fairly straightforward. However, to achieve their high-performance, Questa tools actually generate native code to accelerate simulation performance. Porting to the ARM Neoverse did require adding a new native code generator. This means that the high performance this approach offers has been preserved. This is probably one area where working directly with ARM offered a big advantage.

The server market will not turn on a dime, but the upcoming changes in the overall computing market that will be brought on by increased IoT deployment and also the introduction of 5G will change the landscape dramatically. Some people speculate that mobile and edge devices may actually produce more data than can be ported back to servers, necessitating changes to edge processing and server utilization. ARM seems well positioned to take advantage of these coming changes. EDA users might find common cause with IT teams to take advantage of ARMs new offering to achieve scalability for the most computationally intense applications. More information about this announcement is available on the Mentor website.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.