Through my contacts at SemiWiki I was introduced to a mixed signal IP company named SilabTech, and then decided to interview the founder and CEO, Sujoy Chakravarty.

Sujoy Chakravarty, CEO and Founder

Interview

Q: How did SilabTech get started?

SilabTech was started by 5 ex-TI people. We had prior experience doing these IPs for TI and had some of the industry’s best area/power numbers and ease of SOC integration. We decided to take this out to a mass market on foundry processes and thus got started.

Q: What kinds of IC design are you doing?

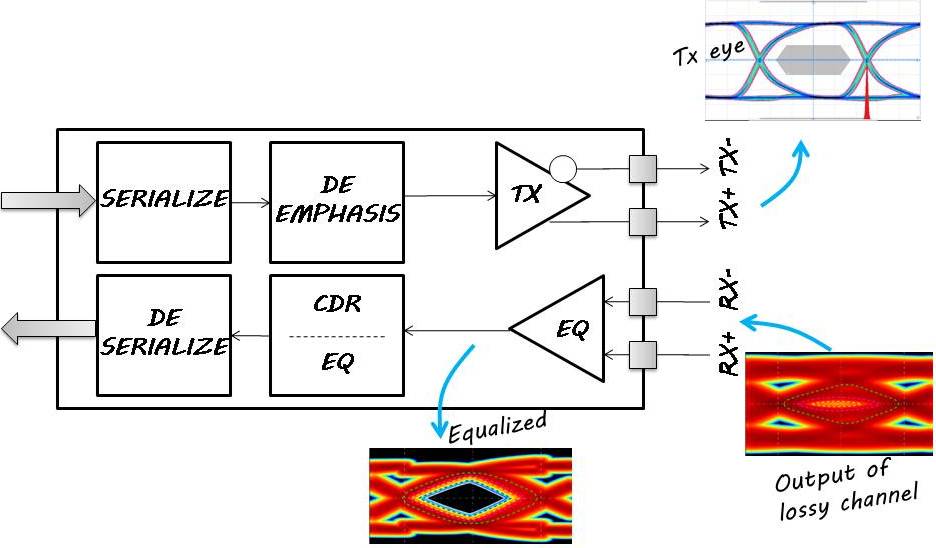

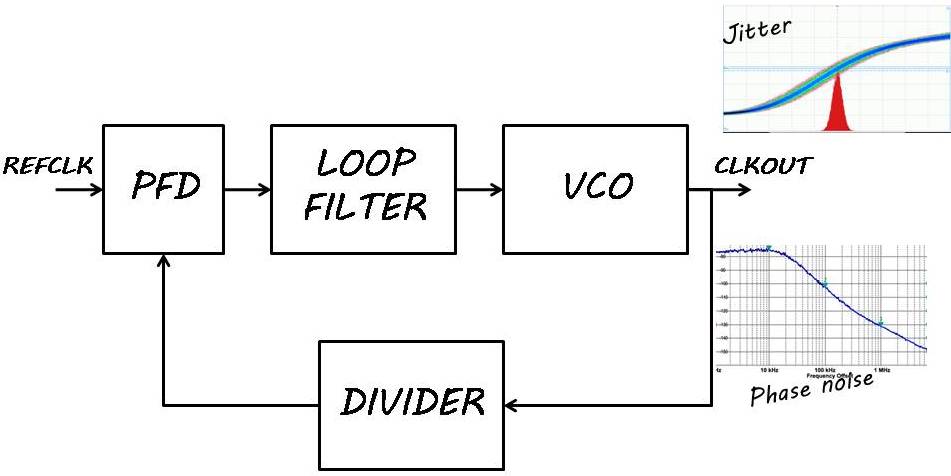

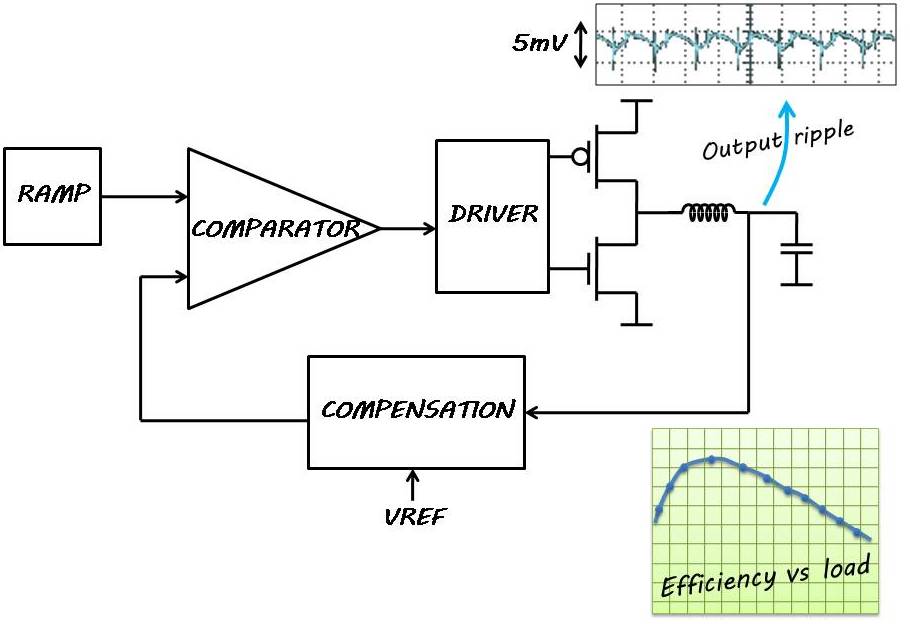

We are a mixed signal IP company and our main offerings are:

Q: Who is buying your physical IP and why?

The customer base for our IP is virtually anyone who builds an SOC.

As more functions get integrated into SOC designs and cost of design vs license increases it makes sense for SOC makers to license IP.

The industry is a little starved for alternatives with domination by big player/(s) and hence a small IP maker who can design the right quality IP and provide good support is exciting.

System designs companies now design their own ASIC and would rather license IP than have in-house designs.

Q: What are the design trends and challenges for AMS IC design that you see?

The major design trend is to combine more functions into the same IP and re-use wherever possible.

Our major challenge is the prohibitive cost of silicon proving an IP in an advanced technology node as well as the cost of EDA associated with this.

Also the need for customization – which drives up the efforts at little or no incremental price.

Q: What EDA tools are used in your IC design flow?

Primarily our EDA tools come from Mentor Graphics. We use:

- Pyxis – IC Layout and Schematics

- Eldo – Circuit simulation

- Calibre – DRC, LVS and extraction

- Questa – digital simulations

- Tessent – DFT

- Expedition – PCB

We also use some Cadence point solutions.

Q: Why did you choose EDA tools from Mentor?

Some tools like Calibre were industry standard and driving us towards Mentor. We got good support and pricing from Mentor for several others and given that they were comparable or better than the competition we chose Mentor.

Q: What was the learning curve like for Pyxis, Eldo and Calibre?

Calibre is the de-facto leader in its space and working with it was easy and painless.

With Eldo we needed to make some adjustments to migrate from Cadence Spectre but did not find it very difficult to do.

Pyxis was a far more complex process. It started from learning a brand new tool, then finding and reporting some rather major issues and getting it to work with all the foundry deliveries. It also took a big change in the normal established Virtuoso flow to set new flows around Pyxis.

Q: How has support been from Mentor?

Mentor support has been excellent. We have onsite dedicated mentor AE support for something like Pyxis and also direct access to Mentor R&D as needed. We have also had several training and QA sessions with Mentor engineering.

Q: What will success look like 12 months from now for SilabTech?

12 months from now SilabTech would have developed, got silicon results and licensed IP in at least 2 advanced technology nodes. These PHY IP from SilabTech will have been proven controller+PHY solutions for USB3.0, PCIe, SATA and MIPI, through partnership built by SilabTech with Controller IP leaders. We would also have one of the worlds lowest power 12Gbps SERDES IP.

Summary

Semiconductor IP companies are in growth mode, and SilabTech is offering mixed-signal IP in three focused areas. Their EDA tool flow uses software from mostly Mentor Graphics plus some Cadence point tools.

lang: en_US

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.