Steve Kommrusch of AMD wrote a white paper with Calypto on how AMD reduced power by 20% on the Jaguar SoC using Calypto’s PowerPro. Dan Nenni blogged about it on SemiWiki back in February here. And now, drumroll, Steve will present the story live and in person at DAC, on Monday June 3rd at 3pm and on Wednesday June 5th at 11am. This is a private suite presentation for which you must register (here).

The AMD Jaguar X86 core is a flexible, high-frequency, processor aimed at system-on-a-chip designs for low- power markets and cloud clients. It uses 28nm process technology and has a small die area (3.1mm[SUP]2[/SUP]). Compared to the previous generation of this core, AMD Bobcat, many blocks were redesigned for improved power efficiency, including the IC loop buffer, store queue, and L2 clocks. The AMD Jaguar compute unit (CU) includes four independent Jaguar cores and a shared-cache unit with four L2 databanks and an L2 interface tile.

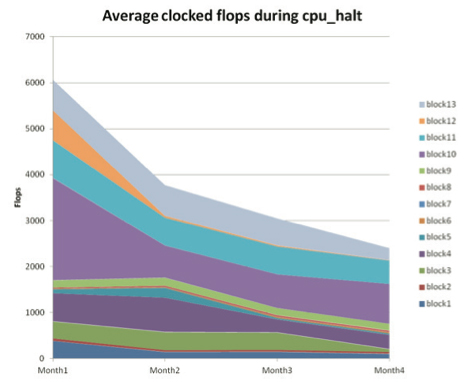

The starting point was the previous design known as Bobcat which was already optimized for power and so already heavily gated. The diagram below shows the number of flops that were still being clocked during a CPU halt, and how this amount decreased over a period of a few months using the PowerPro methdology.

One new block, the shared L2 cache controller, was not from the earlier design. The diagram below shows how the number of flops that are not gated falls dramatically as the focus of doing the design shifts from getting the functionality right to reducing the power.

AMD worked with Calypto to create and efficient RTL clock-gating analysis flow. RTL analysis could run over a weekend and analyze key power benchmark tests. The output was easy for designers to parse and make use of, and included recommendations for improvement and possible optimizations. Correlation between active clock count and total power was good. Ultimately the approach reduced dynamic power by approximately 20%, compared to an already power-optimized design.

Steve was the architect on this design for the clock, reset and power control signals for the Jaguar. All of these products made extensive use of clock gating to improve battery life. Steve’s white paper is available to download from here.

Full details of the DAC presentation, including links to register for either session are on the Calypto website here.

Share this post via:

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center