More so than most aspects of design, power reduction suffers from a paradox that early in the design cycle when the gains are the largest, the accuracy of power estimation is the lowest, and then late in the design cycle, when everything is known pretty much exactly it is too late to make anything other than trivial optimizations. The sweet spot seems to be at the RTL level. There is enough detail in the RTL that reasonable estimates of power can be calculated, but there is flexibility in the RTL (and the associated CPF/UPF power policy files) to be able to make significant savings. Before RTL is available, only rudimentary estimates of power by block are available. After RTL at the gate-level, the estimates are more accurate but the time to make significant changes has passed.

More so than most aspects of design, power reduction suffers from a paradox that early in the design cycle when the gains are the largest, the accuracy of power estimation is the lowest, and then late in the design cycle, when everything is known pretty much exactly it is too late to make anything other than trivial optimizations. The sweet spot seems to be at the RTL level. There is enough detail in the RTL that reasonable estimates of power can be calculated, but there is flexibility in the RTL (and the associated CPF/UPF power policy files) to be able to make significant savings. Before RTL is available, only rudimentary estimates of power by block are available. After RTL at the gate-level, the estimates are more accurate but the time to make significant changes has passed.

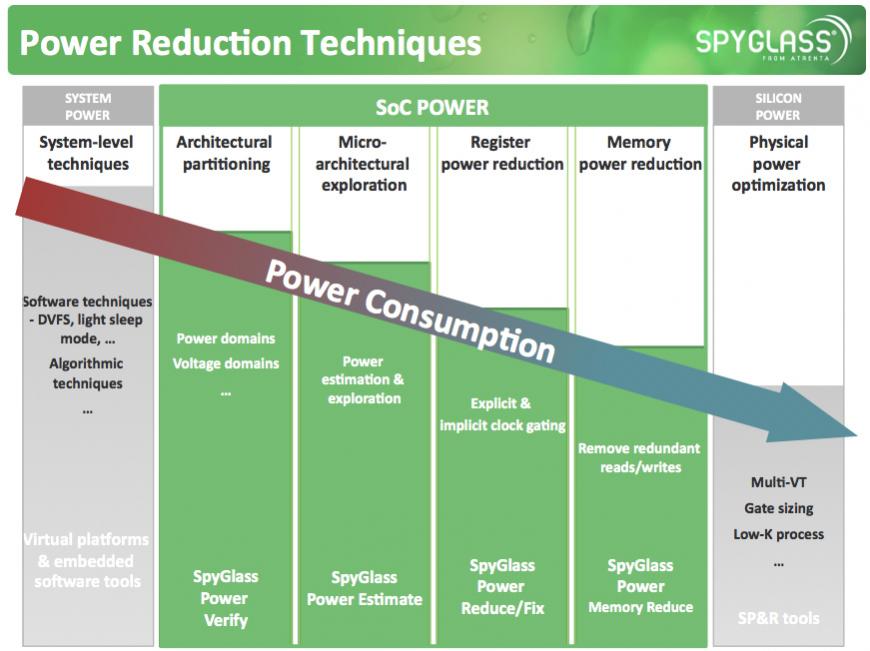

In the architectural stage, virtual platforms can be used to examine the effects of algorithmic techniques and the interaction of software with power reduction features such as powering off unused blocks. Between that, and the implementation flow itself when it is too late to do much more than select appropriate cells from the library and do basic clock gating, Atrenta has a portfolio of tools that can be used to reduce power at the RTL level.

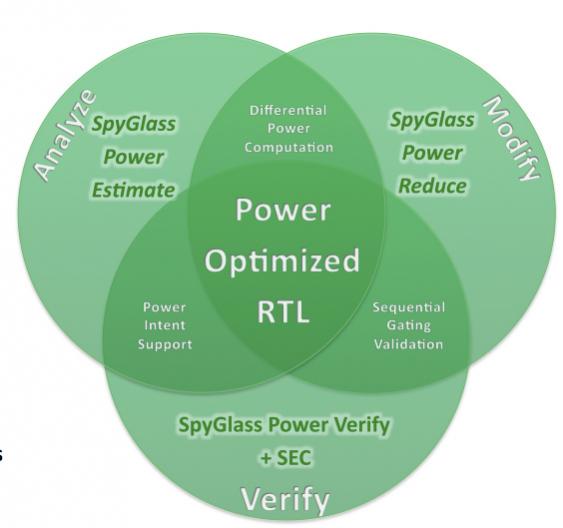

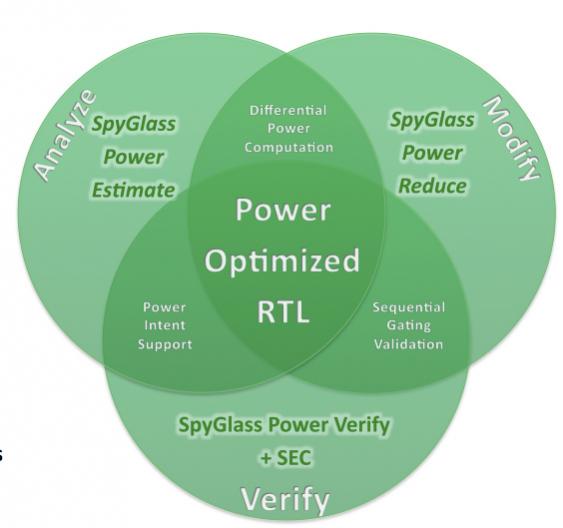

These can be used to do the three different aspects of power optimization: analysis, modification and verification.

SpyGlass Power Verify allows analysis of voltage and power domains. These are, of course, specified in UPF or CPF depending on which toolsets are used for implementation.

SpyGlass Power Estimate allows power estimation and exploration at the RTL level. This requires power vectors since typically the vectors used for functional verification explore lots of corner cases that are not representative of normal behavior.

SpyGlass Power Reduce/Fix performs explicit and automatic sequential clock gating.

SpyGlass Power Memory Reduce removes redundant reads and writes from memory. When the address has not changed to the memory the previous latched value can be used, for example.

Using these tools on representative designs creates power reductions of 15-25% which is significant.

On Thursday this week Atrenta is having a webinar to cover RTL Power Optimization in detail, entitled “The 3 Dimensions of RTL Power Optimization.” It is on April 11th from 8.30am to 9.30am Pacific time. To pre-register go here.

Share this post via:

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era