Hierarchical IC design has been around since the dawn of electronics, and every SoC design today will use hierarchy for both the physical and logical descriptions. During the physical implementation of an SoC you will likely run into EDA tool limits that require a re-structure of the hierarchy. This re-partitioning will cause a change to the logical hierarchy and require some functional verification re-runs.

RTL Restructuring

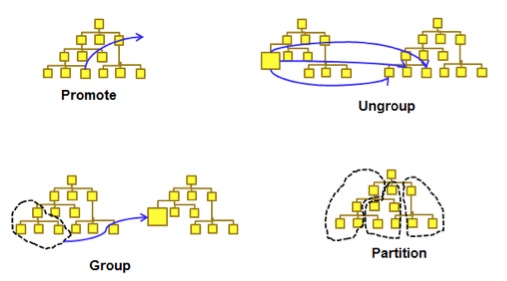

Here are some examples showing a hierarchical design and the different types of restructuring:

For promotion a block is moved from one part of the hierarchy to another part, at a different level. When grouping, several blocks are joined to create a larger, single block. Un-grouping is the reverse of grouping, and lower-level blocks are brought back into the hierarchy.

When making any of these restructuring decisions, the changed design needs to stay connected properly, and that new port names should be legible. You could just manually edit the RTL for your restructuring, but beware of:

- Manual edits causing netlist errors

- Using up valuable designer time

Another approach is to write custom scripts to help automate restructuring. The only downside is that writing scripts takes time and can quickly become more complex and involved than you planned on.

A Restructuring Tool from Atrenta

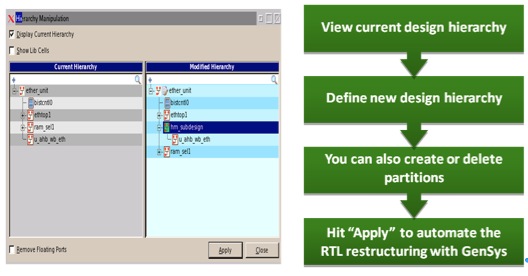

What I love about EDA is that where there is a need, there is probably a tool to help you, and in this case Atrenta has created a tool called GenSys RTL (which reminds me of the tool name Genesis used at Silicon Compilers back in the 1980’s). With this Atrenta tool you can read in RTL (VHDL, SystemVerilog, Verilog), look at the hierarchy, then do restructuring and partitioning:

If your SoC uses a lot of 3rd party IP blocks, or your design team is large, then this type of graphical view of a design will allow you to quickly understand how everything is connected together. The tree widget allows you to traverse the hierarchy and define any needed restructuring, while for users that prefer the command line you can always code in Tcl and batch up your commands as an alternative to interactive use.

Your new hierarchies are automatically created, and all of the details and consistency are automated for you. Just the minimum number of RTL files are actually updated in your design, plus comments are added for you on the changes.

Physical Effects

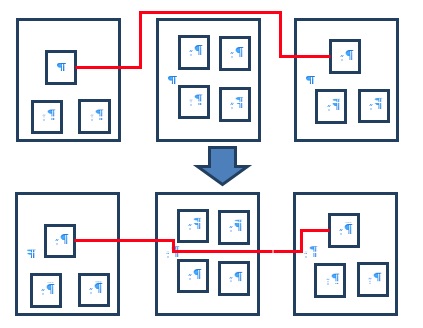

During floor-planning it is common to specify that critical signals be routed through blocks instead of around blocks in order to meet timing specifications.

The GenSys tool lets you quickly add such feed-throughs.

So why spend days to weeks by hand-editing your RTL for re-structuring when you can automate the grunt work with an EDA tool and take only hours of time?

Further Reading

- White Paper: RTL Restructuring. What it is, why you need it and how Atrenta can help, 7 pages by Dr. Bernard Murphy.

Intel, Musk, and the Tweet That Launched a 1000 Ships on a Becalmed Sea