Verification and AMS are top search terms on SemiWiki so clearly designers have a pressing need for fast and accurate verification of today’s mixed-signal SoCs that include massive digital blocks and precision analog/RF circuits. They need simulation performance to verify the mixed-signal functionality, and they need nanometer SPICE accuracy to ensure the SoC meets tight analog/RF specifications.

Current mixed-signal verification solutions are severely compromised. The co-simulation approach worked well for older and simpler designs, but for tightly-integrated analog and digital (big A and big D circuits) they have significant flow and feature limitations. Newer tools based on Verilog-AMS have a well-deserved reputation of being very hard to set up, needing expert-level support. Debugging in Verilog-AMS is often very difficult for SPICE guys, who don’t like programming languages – they prefer to see schematic, netlist, and waveforms – and digital guys don’t want to have to work from an analog design environment.

BDA brings its powerful nanometer circuit verification platform to this problem along with an innovative approach to Verilog-AMS simulation. By focusing on designer’s use models, the BDA solution lets users stay in their preferred flow. Digital designers follow their well-known text-based Verilog use model. Analog designers follow their well-known schematic-based SPICE use model. The underlying powerful simulation and verification capabilities are shared, but designers access them through their usual method of working, without needing lots of training or needing to switch operating paradigm. With this approach it’s very easy for a digital designer to simulate their design using a Verilog-based flow, and replace modules of interest with SPICE netlists. Similarly for the analog designer, they use a SPICE-based flow but easily replace some modules with Verilog or Verilog-AMS netlists.

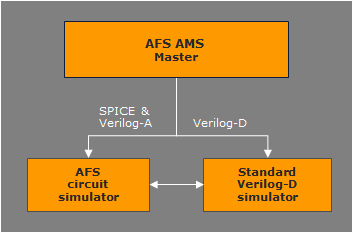

For years AMS tool providers have claimed that “single-kernel” implementations are needed for fast AMS. BDA has dis proven that notion. AFS AMS uses the standard Verilog API to interface to the Verilog simulator. The Verilog simulator is so much faster than even Analog FastSPICE, the API is not a bottleneck. In fact, AFS AMS is blowing away the performance of existing “single-kernel” implementations. The big deal here is not just the performance – it’s that the digital guys can keep using their existing Verilog simulator with the original HDL and testbench along with all of their Verilog simulator’s bells and whistles.

BDA may have broken the logjam in Verilog-AMS verification by making an AMS product so straightforward to set up, so fast to run and so easy to use that it can be useful as an everyday tool.

Also read: A Brief History of SPICE

Share this post via:

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center