Consumer electronics is a new driver in our global semiconductor economy as we enjoy using Smart Phones, Tablets and Ultra Books. The challenge of designing and then verifying the electronic systems to meet the market windows is a daunting one. Instead of starting with a blank sheet for a new product, most electronic design companies are choosing to start with a platform then integrate ready-built IP.

Amazon Kindle Fire – Tear Down

An example of a platform-based consumer product is the Kindle Fire from Amazon. The ICs included in the design of the Kindle Fire are:

- Samsung KLM8G2FEJA 8 GB Flash Memory

- Hynix H9TKNNN4K 512 MB of Mobile DDR2 RAM

- Texas Instruments 603B107 Fully Integrated Power Management IC with Switch Mode Charger

- Texas Instruments LVDS83B FlatLink 10-135 MHz Transmitter

- Jorjin WG7310 WLAN/BT/FM Combo Module

- Texas Instruments AIC3110 Low-Power Audio Codec With 1.3W Stereo Class-D Speaker Amplifier

- Texas Instruments WS245 4-Bit Dual-Supply Bus Transceiver

- 1 GHz processor— a Texas Instruments OMAP 4430

- Texas Instruments WL1270B 802.11 b/g/n Wi-Fi

So, how do you create an SoC like this and what are the costs and power challenges?

DVCon

I spoke with Stephen Bailey of Mentor Graphics this week to learn about a half-day tutorial that he is part of at DVcon called: Design & Verification of Platform-Based, Multi-Core SoCs. Platform-based design is when you create a new SoC with pre-defined processor subsystems (think ARM), semi IP, and then add some of your own new blocks (maybe as little as 10% of the design).

Stephen Bailey, Director of Product Marketing, Mentor Graphics DVT

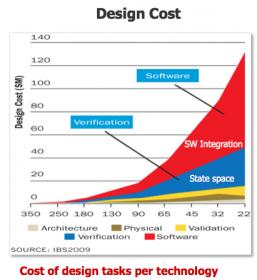

Clearly SW integration is now the bottleneck and with an exploding amount of state space it makes verification an issue to automate.

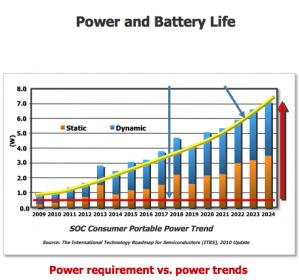

We all love our mobile devices to have a battery life of at least one full business day, so we need to design with that constraint in mind.

Tools and Methodology

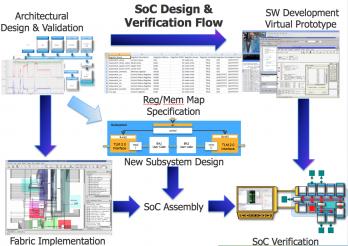

Here’s a methodology flow that can help address the design and verification challenges listed so far:

Specific EDA tools for each block show above:

- Vista for SoC architectural design and SW development virtual prototyping;

- Certe for register-memory map specification;

- Catapult for HLS of the new subsystem and Calypto for sequential LEC;

- ARM’s AMBA Designer for Fabric implementation

- Questa for simulation (with Vista for SC/TLM, new subsystem verification pre/post HLS and sign-off verification of the SoC);

- Veloce for sign-off verification (SoCs require far more cycles than is practical with SW simulation alone) and SW development;

- We also use Questa/Veloce Verification IP, inFact with VIP to create traffic generators to verify (re-validate) performance at RTL, and Codelink for synchronized SW/HW debug in both Questa and Veloce

- Codebench embedded software tools that can be used with SW virtual prototype, CDC and Power-Aware verification. However, due to time constraints, we only can only mention them as part of the complete flow.

Summary

To learn more about design and verification of platform-based, multi-core SoCs then consider attending the half-day tutorial at DVCon on March 1 in San Jose. You’ll hear from experts at three different companies:

- Paul Martin, ARM, Inc.

- Bryan Bowyer, Calypto Design Systems, Inc.

- Mark Peryer, Verification Methodologist Mentor Graphics

- Jim Kinney, Mentor Graphics

- Shabtay Matalon, ESL Market Development Manager, Mentor Graphics

The tutorial will cost you $75 and in return you receive the slides on a USB drive and they feed you lunch and provide coffee.

Comments

0 Replies to “Design & Verification of Platform-Based, Multi-Core SoCs”

You must register or log in to view/post comments.