Semiconductor intellectual property (IP) plays a critical role in modern system-on-chip (SoC) designs. That’s not surprising given that modern SoCs are highly complex designs that leverage already proven building blocks such as processors, interfaces, foundational IP, on-chip bus fabrics, security IP, and others. This… Read More

Synopsys Presents AI-Fueled Innovation at SNUG 2024

SNUG is the premier event for Synopsys to showcase its technology and impact on the industry. This year’s SNUG did not disappoint. The two-day event packed many fantastic user presentations along with exciting news of innovation from Synopsys. Jensen Huang and Sassine Ghazi even held a live, interactive Q&A session. Compelling… Read More

Scaling Data Center Infrastructure for the Terabit Era

Earlier this month, SemiWiki wrote about Synopsys’s complete 1.6T Ethernet IP solution to drive AI and Hyperscale Data Center chips. A technology’s success is all about when, where and how it gets adopted within the ecosystem. In the high-speed ethernet ecosystem, the swift adoption of 1.6T Ethernet relies on key roles and coordinated… Read More

TSMC and Synopsys Bring Breakthrough NVIDIA Computational Lithography Platform to Production

NVIDIA cuLitho Accelerates Semiconductor Manufacturing’s Most Compute-Intensive Workload by 40-60x, Opens Industry to New Generative AI Algorithms.

An incredible example of semiconductor industry partnerships was revealed during the Synopsys User Group (SNUG) last month. It started with a press release but there is much… Read More

Synopsys SNUG Silicon Valley Conference 2024: Powering Innovation in the Era of Pervasive Intelligence

After the leadership transition at the top, Synopsys had just a little more than two months before the company’s flagship event, the Synopsys User Group (SNUG) conference. The Synopsys user community and entire ecosystem were waiting to hear new CEO Sassine Ghazi’s keynote to learn where the company is going and its strategic … Read More

2024 DVCon US Panel: Overcoming the challenges of multi-die systems verification

2024 DVCon was very busy this year. Bernard Murphy and I were in attendance for SemiWiki, he has already written about it. Multi die and chiplets was again a popular topic. Lauro Rizzatti, a consultant specializing in hardware-assisted verification, moderated an engaging panel, sponsored by Synopsys, focusing on the intricacies… Read More

Synopsys Enhances PPA with Backside Routing

Complexity and density conspire to make power delivery very difficult for advanced SoCs. Signal integrity, power integrity, reliability and heat can seem to present unsolvable problems when it comes to efficient power management. There is just not enough room to get it all done with the routing layers available on the top side… Read More

Podcast EP212: A View of the RISC-V Landscape with Synopsys’ Matt Gutierrez

Dan is joined by Matt Gutierrez. Matt joined Synopsys in 2000 and is currently Sr. Director of Marketing for Processor & Security IP and Tools. His current responsibilities include the worldwide marketing of ARC Processors and Subsystems, Security IP, and tools for the development of application-specific instruction … Read More

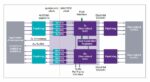

Complete 1.6T Ethernet IP Solution to Drive AI and Hyperscale Data Center Chips

The demand for high-bandwidth, low-latency networking solutions has never been greater. As artificial intelligence (AI) workloads continue to grow exponentially, and hyperscale data centers become the backbone of our digital infrastructure, the need for faster and more efficient communication technologies becomes imperative.… Read More

2024 Signal & Power Integrity SIG Event Summary

It was a dark and stormy night here in Silicon Valley but we still had a full room of semiconductor professionals. I emceed the event. In addition to demos, customer and partner presentations, we did a Q&A which was really great. One thing I have to say is that Intel really showed up for both DesignCon and the Chiplet Summit. Quite… Read More