At #61DAC our very own Daniel Nenni from SemiWiki moderated an informative panel discussion on the topic of 3D IC Design Ecosystem. Panelists included: Deepak Kulkarni – AMD, Lalitha Immaneni – Intel Foundry, Trupti Deshpande – Qualcomm, Rob Aitken – CHIPS, Puneet Gupta – UCLA, Dragomir Milojevic – imec. Each panelist had a brief… Read More

Podcast EP238: Intel Capital’s Focus on Improving the Future of Semiconductors with Jennifer Ard

Dan is joined by Jennifer Ard, Intel Capital Managing Director and Head of Investment Operations. In her role, Jen is responsible for managing Intel Capital’s investment-related operations. Additionally, she is primarily focused on investing in silicon-related companies and has been involved in multiple deals including… Read More

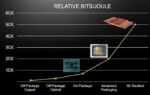

Intel’s Gary Patton Shows the Way to a Systems Foundry #61DAC

#61DAC was buzzing this year with talk of AI and multi-die, heterogeneous design. The promise of making 2.5/3D design and a chiplet ecosystem mainstream reality was the focus of a lot of the panels and presentations at the conference. AI is certainly a driver for this new design style, but the conversation was broader than just AI,… Read More

The Case for U.S. CHIPS Act 2

Despite murky goals and moving targets, the recent CHIPS Act sets the stage for long term government incentives.

Authored by Jo Levy and Kaden Chaung

On April 25, 2024, the U.S. Department of Commerce announced the fourth, and most likely final, grant under the current U.S. CHIPS Act for leading-edge semiconductor manufacturing.… Read More

Intel is Bringing AI Everywhere

On April 8 and 9 Intel held its Intel Vision event in Phoenix Arizona. This is Intel’s premier event for business and technology executive leaders to come together and learn about the latest industry trends and solutions in advancements from client, to edge, to data center and cloud. The theme of this year’s event was Bringing AI … Read More

Intel and TSMC IDM 2024 Discussions

In December 2023, we published the Intel Revenue forecast for external wafer sales, gave a breakdown on how customers plan to ramp the foundry. The forecast is still valid (it assumes Intel executes on all plans) but since then we have a better understanding of Intel’s strategy and scenarios that could unfold.

The scenarios… Read More

Intel Direct Connect Event

On Wednesday, February 21st Intel held their first Foundry Direct Connect event. The event had both public and NDA sessions, and I was in both. In this article I will summarize what I learned (that is not covered by NDA) about Intel’s business, process, and wafer fab plans (my focus is process technology and wafer fabs).

Business

… Read MoreISS 2024 – Logic 2034 – Technology, Economics, and Sustainability

For the 2024 SEMI International Strategy Symposium I was challenged by members of the organizing committee to look at where logic will be in ten years from a technology, economics, and sustainability perspective. The following is a discussion of my presentation.

To understand logic, I believe it is useful to understand what makes… Read More

Intel should be the Free World’s Plan A Not Plan B, and we need the US Government to step in

There are trillions of dollars at stake with AI and huge geopolitical consequences. However, the weak foundation to American technological power is their dependence on Taiwan and TSMC, which is where most advanced silicon is manufactured. America has also been taking China to the ropes lately in their economic/technology proxy… Read More

How Disruptive will Chiplets be for Intel and TSMC?

Chiplets (die stacking) is not new. The origins are deeply rooted in the semiconductor industry and represent a modular approach to designing and manufacturing integrated circuits. The concept of chiplets has been energized as a response to the recent challenges posed by the increasing complexity of semiconductor design. … Read More