Artificial intelligence (AI) is transforming every layer of computing, from hyperscale data centers training trillion-parameter models to battery-powered edge devices performing real-time inference. Hardware requirements are escalating on every front: compute density is increasing, power budgets are tightening, … Read More

Semiconductor Intellectual Property

The RISC-V Revolution: Insights from the 2025 Summits and Andes Technology’s Pivotal Role

RISC-V has emerged as a cornerstone of modern computing, offering an open-source alternative to proprietary designs like ARM and x86. Free from licensing fees and highly extensible, RISC-V powers everything from IoT devices to AI accelerators, with over 13 billion cores shipped globally. Annual RISC-V Summits, organized… Read More

A Remote Touchscreen-like Control Experience for TVs and More

How do you control your smart TV? With a remote control of course, already quite capable since it allows voice commands to find a movie or TV show without needing all that fiddly button-based control and lookup. But there’s a range of things you can’t do that we take for granted on a tablet or phone screen. Point and click on an object,… Read More

Podcast EP309: The State of RISC-V and the Upcoming RISC-V Summit with Andrea Gallo

Daniel is joined by Andrea Gallo, CEO of RISC-V International. Before joining RISC-V he worked in leadership roles at Linaro for over a decade and before Linaro he was a fellow at STMicroelectronics.

Dan explores the current state of the RISC-V movement with Andrea, who describes the focus and history of this evolving standard.… Read More

Thalia and X-FAB Forge Strategic Partnership to Safeguard Supply and Accelerate IP Migration

In a move that underscores the semiconductor industry’s push toward resilient supply chains and agile innovation, Thalia Design Automation and X-FAB Silicon Foundries have announced a strategic partnership aimed at safeguarding supply continuity and accelerating intellectual property (IP) migration. This collaboration,… Read More

AI Everywhere in the Chip Lifecycle: Synopsys at AI Infra Summit 2025

At the AI Infra Summit 2025, Synopsys showed how artificial intelligence has become inseparable from the process of creating advanced silicon. The company’s message was clear: AI is an end-to-end engine that drives every phase of chip development. Three Synopsys leaders illustrated this from distinct vantage points. Godwin… Read More

Analog Bits Steps into the Spotlight at TSMC OIP

The TSMC Open Innovation Platform (OIP) Ecosystem Forum kicked off on September 24 in Santa Clara, CA. This is the event where TSMC recognizes and promotes the vast ecosystem the company has created. After watching this effort grow over the years, I feel that there is nothing the group can’t accomplish thanks to the alignment and… Read More

Yuning Liang’s Painstaking Push to Make the RISC-V PC a Reality

At Embedded World 2025 in Nuremberg, Germany, on March 11, 2025, Yuning Liang, DeepComputing Founder and CEO walked onto the stage with a mischievous smile and a challenge. “What’s the hardest product to make?” he asked rhetorically. “A laptop. It’s bloody hard… but we did it. You can swap the motherboard, you can upgrade, you can’t… Read More

Arm Lumex Pushes Further into Standalone GenAI on Mobile

When I first heard about GenAI on mobile platforms – from Arm, Qualcomm and others – I confess I was skeptical. Surely there wouldn’t be enough capacity or performance to deliver more than a proof of concept? But Arm, and I’m sure others, have been working hard to demonstrate this is more than a party trick. It doesn’t hurt that foundation… Read More

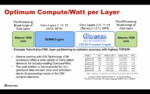

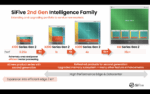

SiFive Launches Second-Generation Intelligence Family of RISC-V Cores

SiFive, founded by the original creators of the RISC-V instruction set, has become the leading independent supplier of RISC-V processor IP. More than two billion devices already incorporate SiFive designs, ranging from camera controllers and SSDs to smartphones and automotive systems. The company no longer sells its own chips,… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?