The Electronic Design Process Symposium is an annual workshop run by the IEEE Computer Society of Silicon Valley and the IEEE Council on Electronic Design Automation. I presented there because it’s devoid of product marketing pitches, and is two days of discussion on technical and process issues in SoC design. My slides are here:… Read More

Semiconductor Intellectual Property

Shorten Time to Market for NVM Express Based Storage Solution

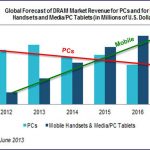

A number of technical and business trends are converging to create a booming market for solid state drives (SSDs), with gigabytes of flash memory capacity along with the related control electronics packaged in the form factor of a 1.8”‐, 2.5”‐ or 3.5”. storage device. The first is the emergence of tablets and pervasiveness of smart… Read More

ARM Results, Strong Biceps

ARM announced their Q1 results yesterday. Having just written that Intel lost $1B in mobile, I guess I could have used the title “ARM didn’t lose $1B in mobile.” They made $100M (on revenues of $300M). So let’s start off with what their results actually were and then look at what other things of interest … Read More

Welcome, LPDDR4!

Thanks to memory controller expert Marc Greenberg, Marketing Director for DDRn Controller IP with Synopsys, for this post “Qualcomm announces first application processor with LPDDR4 capability”. According with Marc, this Application Processor, the Snapdragon 810, is “the first product that I’m aware of that will use LPDDR4… Read More

On-chip Firewall

We have had the Snowden revelations that the NSA has gone rogue, Target lost a zillion credit cards, the Heartbleed bug meaning that main security protocol of the internet had been coded up wrong for a couple of years, theft of records from RSA and more. One result is that people do not completely trust a security system that depends… Read More

NVM central to multi-layer trust in cloud

Pop quiz: Name one of the hottest applications for non-volatile memory – A) processor and code configuration; B) RFID tags; C) secure encryption keys; D) all the above. The answer is D, but not in the way you may be thinking; a new approach is using all these ideas at once, combined in SoC designs targeting advanced security … Read More

Sensor clusters at edge call for NoCs nearby

In his recent blog on EETimes, Kurt Shuler of Arteris took a whimsical look at the hype surrounding the IoT, questioning the overall absence of practicality and a seemingly misplaced focus on use cases at the expense of a coherent architecture. I don’t think it is all that bleak, but when it comes to architecture, Kurt is right, and… Read More

Does Processor IP still get the Lion’s share in 2013?

I think that the answer is pretty obvious, but the interesting point is to figure out which processor type, and which part of revenues, up-front license or royalties? One of my customers, let’s call him Mr. X, ask me to clarify this point. Mr. X has bought the excellent report from Gartner “Market Share: Semiconductor Design Intellectual… Read More

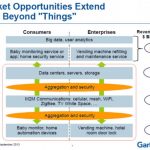

Will IoT Drive the Next Semiconductor Revolution?

To further my quest to comprehend the latest trends in the semiconductor industry continues, I spent the morning with SEMI at the “The Silicon Valley Breakfast Forum: Internet of Things (IoT) – Driving the Microelectronics Revolution” seminar. I’m a big fan of the breakfast seminar concept. I’m up early anyway and it is … Read More

4G shalt thou not count, neither count thou 2G

Five years from now, what will be the leading mobile connectivity standard? If you said 4G, please report to the brainwashing remediation center nearest you immediately. 3G is not only here to stay for the long haul, it’s growing – and will quickly become the preferred choice for M2M deployments.… Read More

Crossing the Yield Cliff: IDP V6 and the Future of Manufacturing Forecasting