Today Sonics announced the latest version of their network-on-chip (NoC) technology, SonicsGN-3.0. As with any new release there are lots of improvements that are of interest mainly to existing users, but the big area with increased capability is the expanded interleaved memory technology (IMT). This was first introduced … Read More

Semiconductor Intellectual Property

Apple Watch Design Revisit with a Wi-Fi Twist

Apple Watch is the world’s most celebrated gadget in 2015. At the same time, however, early product reviews highlight some issues about slow apps, less than impressive user experience, and short battery life.

Apple, the master of artful integration, has done well for its reputation of elite hardware and has been able to … Read More

New Tool Suite to Accelerate SoC Integration

Today, an SoC is seen in the context of an optimized assembly of IPs; it’s no more a single monolithic chip design. It’s very common to see an ARM processor IP along with an interconnect IP, a memory IP, and couple of buses and interfaces IP in an SoC. Although the SoC seems to be an integrated collection of IPs, it can be very complex and… Read More

Design Data Management: An Analog IP Porting Case Study

IQ-Analog Corp. offers “off-the-shelf” data converter intellectual property (IP) for multiple foundries. The San Diego, California–based semiconductor design firm also provides analog front-end (AFE) technology that it tailors according to customer needs. And that’s where the dilemma begins.

IQ-Analog’s… Read More

ARM and frog Team up with UNICEF to Foster Creation of Wearables for the Developing World

When the term wearables is mentioned most people’s first thoughts go to devices like the Apple Watch, Fitbit Flex, or Nike Fuel Band. Wearables such as these solve first-world problems like how much exercise am I getting, or what is my heart rate. The developed world drives the development of new technology in most cases, and wearables… Read More

Vacationing with the Fabless Semiconductor Ecosystem!

The Design Automation Conference is the largest and most diverse event in the fabless semiconductor ecosystem. Next week in San Francisco you will see technology and people you have never seen before. You will benefit from the efforts of hundreds of thousands of semiconductor professionals like myself who have dedicated their… Read More

MIPI Beyond Mobile, Semiwiki Blogger Paper at #52DAC!

IoT or wearable: it’s fascinating to see how many articles, blogs, and comments have been posted about them during the last two years! IoT business potential is huge as are the number of possible applications. If we summarize the functions within a wearable system we can count:

[LIST=1]

Even More Integration and Automation for ARM-based Designs

The attraction to an IP-based design methodology is that you can assemble an SoC from ready-made IP blocks, saving you valuable engineering development and verification time, while reducing risks from having to develop something from scratch and hoping that they meet industry standard specs. ARM is well known for supplying … Read More

Ultra-Low Power Non-Volatile Memory Solutions for the Smart Connected Universe

DAC is a great place to gather information about products and technologies. However it can be difficult to chase down the information you need because you may need to cover a lot of ground to hear or talk to the people with the right knowledge. Fortunately there are a few places you can go to learn about a number of products at one place.… Read More

The Trojan Horse Was Free Too

Timeo Danaos et dona ferentes. I fear the Greeks especially when bearing gifts. In Virgil’s Aeneid these words are spoken by the Trojan priest Laocoön warning about the wooden horse that the Greeks have offered Troy. But to no avail, Laocoön is slain by serpents and the Trojans bring the horse inside the walls of Troy. Since… Read More

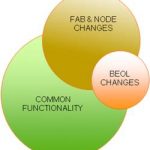

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era