The Electronic Design Process Symposium (EDPS) is April 18 & 19 in Monterey. The workshop style Symposium is in its 20[SUP]th[/SUP] year. The first session is titled “ESL & Platforms”, which immediately follows the opening Keynote address by Ivo Bolsens, CTO of Xilinx.

In his keynote presentation Ivo will present how… Read More

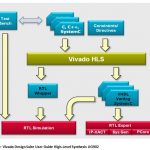

High Level Synthesis – It’s for Real

It was spring 2010 and I was asked to attend an HLS (High Level Synthesis) meeting. To be honest I cringed, after my bad relationship with Accel DSP and broken promises my heart was all walled up and needed counseling. But my management had a way of making me an offer I could not refuse, like keeping my job. So reluctantly I went. Does your… Read More

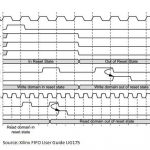

A Non Deterministic Timing Problem

When I was not messing around with FPGA Research and Development, or Algorithms, I was often called into the lab or field and presented this type of scenario… Most of the time, the fix was the same…

At least a few times a year, I’d get the call. Sometimes a panic in the voice, or sometimes defeat. And who wouldn’t be defeated? After… Read More

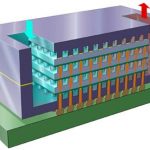

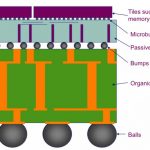

3D Architectures for Semiconductor Integration and Packaging

There is obviously a lot going on in 3D IC these days. And I don’t mean at the micro level of FinFETs which is also a way of going vertical. I mean through-silicon-via (TSV) based approaches for either stacking die or putting them on an interposer. Increasingly the question is no longer if this technology will be viable (there… Read More

Xilinx Programmable Packet Processor

At the Linley conference last week I ran into Gordon Brebner of Xilinx. He and I go a long way back. We had adjacent offices in Edinburgh University Computer Science Department back when we were doing our PhDs and conspiring to network the department’s Vax into the university network over a two-week vacation. We managed to … Read More

3D-IC Physical Design

When process nodes reached 28 nm and below, it appeared that design density is reaching a saturation point, hitting the limits of Moore’s law. I was of the opinion that the future of microelectronic physical design was limited to 20 and 14 nm being addressed by technological advances such as FinFETs, double patterning, HKMG (High-k… Read More

Xilinx and Altera’s Summer At The Beach

The “old saw” is “To Sell in May and Go Away.” It’s a Maxim that particularly applies to semiconductor stocks as they typically drop from a post April earnings peak through the summer doldrums to a late September nadir only to be revived in the prelude of October earnings. It has happened again this year, although the path taken by the… Read More

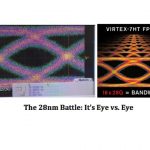

Altera and Xilinx Eyeing 28nm FPGA Dominance

28nm FPGAs are finally hitting the market and the next round in the battle between Altera and Xilinx is heating up. At 40nm, Altera beat Xilinx out the door by a year and as a consequence won a lot of new sockets in the high end Communications market. In the past year, Altera has closed the revenue and market share gap with Xilinx. This … Read More

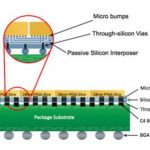

The World’s Smallest Printed Circuit Boards: interposers

Have you ever had the experience where you look up some unusual word in the dictionary since you don’t remember seeing it before. And then, in the next few weeks you keep coming across it. Twice in the last week I have been in presentations about the economics of putting die onto silicon interposers and the possibility of a new… Read More

Is Intel About to Take Flight?