This year Cadence Design Systems is showcasing system design enablement in their booth, capitalizing on the industry shift from naked chip design to system level chip design. Apple started it with making the chips inside the iProducts as part of the system and now other systems companies are looking to take more control over their… Read More

Mentor a Siemens Business @#54thDAC

This year the Mentor booth will be quite interesting now that they are part of Siemens. I expect zero changes to their DAC presence but we shall see. It will certainly be good to see Wally again. More importantly, I will be afforded the opportunity to talk personally with both Wally Rhines, CEO of Mentor ANDChuck Grindstaff executive… Read More

Photonics at DAC – Integrated Electronic/Photonic Design Flow to be Presented at Cadence Theater

I recently wrote an article on SemiWiki talking about the integrated Electronic/Photonic Design Automation (EPDA) flow that is being developed by Cadence Design Systems, Lumerical Solutions and PhoeniX Software and how that flow is now expanding into the system level through SiP (system in package) techniques.

Up till recently,… Read More

Webinar: Achieving Very High Bandwidth Chip-to-Chip Communication with the Interlaken Interface Protocol

Open Silicon will hold this webinar on June 13th at 8 am PDT (or 5 pm CE) to describe their Interlaken IP core, and how to achieve very high bandwidth C2C communication in various networking applications. To be more specific, the Interlaken protocol can be used to support Packet Processing/NPU, Traffic Management, Switch Fabric,… Read More

Consolidation and Design Data Management

Consensia, a Dassault Systemès channel partner, recently hosted a webinar on DesignSync, a long-standing pillar of many industry design flows (count ARM, Qualcomm, Cavium and NXP among their users). A motivation for this webinar was the impact semiconductor consolidation has had on the complexity of design data management,… Read More

Webinar -New Concepts in Semiconductor IP Lifecycle Management

The semiconductor IP market continues growing at a healthy rate, and IP reuse is a staple of all modern SoC designs. Along with the acceptance of IP reuse comes a host of growing challenges, like:

- Increase in design files

- Increase in meta-data

- More links between design members worldwide

- More links between data in multiple engineering

Webinar: Getting to Accurate Power Estimates Earlier and Faster

Power has become a very important metric in modern designs – for mobile and IoT devices which must live on a battery charge for days or years, for datacenters where power costs can be as significant as capital costs, and for increasingly unavoidable regulatory reasons. But accurate power estimation on a design must start from an … Read More

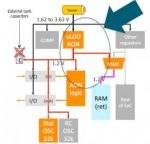

Webinar: Recipe to consume less than 0.5 µA in sleep mode

Dolphin is addressing the ultra-low-power (ULP) needs for some applications, like for example Bluetooth low energy (BLE), machine-to-machine (M2M) or IoT edge devices in general. For these applications, defining active and sleep modes is imperative, but it may not be enough to guarantee that the battery-powered system will… Read More

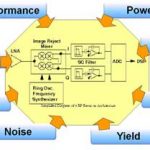

Webinar – Low Power Circuit Sizing for IoT

Optimizing analog designs has always been a difficult and tricky process. Designing for IoT applications has only made this more difficult with the added importance of minimizing power. Unlike other circuit parameters, it is not easy to specify power as a design goal when using equations. Power is a resultant property and must… Read More

Understanding ISO 26262 Compliance for Automotive Suppliers

The semiconductor, IP, Software and EDA industries are all focusing on the growing automotive market because of its electronic content, size and growth. There are long-time suppliers to the automotive industry, and also first-time vendors that are launching something new every week for electronics in automotive. So where … Read More

Crossing the Yield Cliff: IDP V6 and the Future of Manufacturing Forecasting