Synopsys recently held a webinar session on this topic and Gustavo Pimentel, Principal Product Marketing Manager at the company led the webinar session. Going into the webinar session, I found myself wondering: why focus on PCIe 5.0, eight years after its release? With the industry buzzing about Edge AI, cloud computing, and … Read More

Synopsys and TSMC Unite to Power the Future of AI and Multi-Die Innovation

In a rapidly evolving semiconductor landscape, where AI demands unprecedented computational power and efficiency, Synopsys has deepened its partnership with TSMC to pioneer advancements in AI-driven designs and multi-die systems. Announced during the TSMC OIP Ecosystem Summit last week, this collaboration leverages … Read More

AI Everywhere in the Chip Lifecycle: Synopsys at AI Infra Summit 2025

At the AI Infra Summit 2025, Synopsys showed how artificial intelligence has become inseparable from the process of creating advanced silicon. The company’s message was clear: AI is an end-to-end engine that drives every phase of chip development. Three Synopsys leaders illustrated this from distinct vantage points. Godwin… Read More

Synopsys Collaborates with TSMC to Enable Advanced 2D and 3D Design Solutions

Synopsys has deepened its collaboration with TSMC certifying the Ansys portfolio of simulation and analysis tools for TSMC’s cutting-edge manufacturing processes including N3C, N3P, N2P, and A16. This partnership empowers chip designers to perform precise final checks on designs, targeting applications in AI acceleration,… Read More

Synopsys Announces Expanding AI Capabilities and EDA AI Leadership

In the fast-paced semiconductor industry Synopsys has redefined EDA with its Synopsys.ai Copilot, a generative AI tool. Since its launch in November 2023, and yes I was at the launch and very skeptical, Copilot has evolved to address the industry’s growing design complexity and projected 15-30% workforce gap by 2030. Let’s… Read More

The Rise, Fall, and Rebirth of In-Circuit Emulation (Part 1 of 2)

Introduction: The Historical Roots of Hardware-Assisted Verification

The relentless pace of semiconductor innovation continues to follow an unstoppable trend: the exponential growth of transistor density within a given silicon area. This abundance of available semiconductor fabric has fueled the creativity of design… Read More

eBook on Mastering AI Chip Complexity: Pathways to First-Pass Silicon Success

The rapid evolution of artificial intelligence (AI) is transforming industries, from autonomous vehicles to data centers, demanding unprecedented computational power and efficiency. As highlighted in Synopsys’ guide, the global AI chip market is projected to reach $383 billion by 2032, growing at a 38% CAGR. This … Read More

448G: Ready or not, here it comes!

The march toward higher-speed networking continues to be guided by the same core objectives as has always been : increase data rates, lower latency, improve reliability, reduce power consumption, and maintain or extend reach while controlling cost. For the next generation of high-speed interconnects, these requirements … Read More

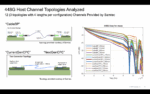

Synopsys Webinar – Enabling Multi-Die Design with Intel

As we all know, the age of multi-die design has arrived. And along with it many new design challenges. There is a lot of material discussing the obstacles to achieve more mainstream access to this design architecture, and some good strategies to conquer those obstacles. Synopsys recently published a webinar that took this discussion… Read More

Synopsys FlexEDA: Revolutionizing Chip Design with Cloud and Pay-Per-Use

On July 9, 2025, Vikram Bhatia, head of product management for Synopsys’ cloud platform, and Sashi Obilisetty, his R&D engineering counterpart, presented a DACtv session on Synopsys FlexEDA, as seen in the YouTube video. Drawing from three and a half years of data, the session showcased how this cloud-based, pay-per-use… Read More