While this iconic advertising phrase was first used to describe the ink reliability of a ballpoint pen, it perfectly summarizes the average consumer’s attitude toward automobile reliability as well. We don’t really care how it’s done, as long as everything in our car works first time, every time. Even when that includes heated… Read More

Yawn… New EDA Leader Results Are Coming

We will soon start to see the quarterly financial reporting installments of the “Big 3” public EDA companies. I predict they will be as boring as usual. I am not sure if I would want it any differently though.

Back in the 90s there were times when it was truly interesting to wait to see what Cadence, Mentor, or later Synopsys, might announce.… Read More

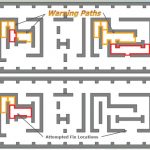

Fixing Double-patterning Errors at 20nm

David Avercrombie of Mentor won the award for the best tutorial at the 2012 TSMC OIP for his presentation, along with Peter Hsu of TSMC, on Finding and Fixing Double Patterning Errors in 20nm. The whole presentation along with the slides is now available online here. The first part of the presentation is an introduction to double … Read More

Mentor @ the TSMC Open Innovation Platform Forum

At TSMC’s Open Innovation Platform (OIP) Ecosystem Forum, Mentor made technical presentations on four different topics, two of them co-presented with TSMC and LSI Corporation. Those presentations are described below with links to downloadable pdf presentation files.

Finding and Fixing Double Patterning Errors in… Read More

Winner, Winner, Chicken Dinner!

I have no idea if chicken was actually on the menu, but on December 12, Calibre RealTime picked up its thirdindustry award, this time the 2012 Elektra Award for Design Tools and Development Software from the European Electronics Industry. Calibre RealTime came out on top in a group full of prestigious finalists, including ByteSnap,… Read More

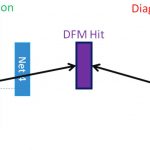

IP Scoring Using TSMC DFM Kits

Design For Manufacturing (DFM) is the art and science of making an IC design yield better in order to receive a higher ROI. Ian Smith, an AE from Mentor in the Calibre group presented a pertinent webinar, IP Scoring Using TSMC DFM Kits. I’ll provide an overview of what I learned at this webinar.… Read More

Double Patterning Tutorial

Double patterning at 20nm is one of those big unavoidable changes that it is almost impossible to know too much about. Mentor’s David Abercrombie, DFM Program Manager for Calibre, has written a series of articles detailing the multifaceted impacts of double patterning on advanced node design and verification. There is… Read More

Yield Analysis and Diagnosis Webinar

Sign up for a free webinar on December 11 on Accelerating Yield and Failure Analysis with Diagnosis.

The one hour presentation will be delivered via webcast by Geir Eide, Mentor’s foremost expert in yield learning. He will cover scan diagnosis, a software-based technique, that effectively identifies defects in digital logic… Read More

Double Patterning Exposed!

Wanna become the double patterning guru at your company? David Abercrombie, DFM Program Manager for Calibre, has written a series of articles detailing the multifaceted impacts of double patterning on advanced node design and verification. For designers struggling to understand the complexity and nuances of double patterning,… Read More

GLOBALFOUNDRIES and Mentor Develop Methods to Identify Critical Features in IC Designs

Since the beginning of the semiconductor industry, improving the rate of yield learning has been a critical factor in the success silicon manufacturing. Each fab has dedicated yield teams that look at the yield of wafers manufactured the previous day and attempt to find the root cause of any unexpected “excursions.” In earlier… Read More