You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 159

[name] => Siemens EDA

[slug] => siemens-eda

[term_group] => 0

[term_taxonomy_id] => 159

[taxonomy] => category

[description] =>

[parent] => 157

[count] => 828

[filter] => raw

[cat_ID] => 159

[category_count] => 828

[category_description] =>

[cat_name] => Siemens EDA

[category_nicename] => siemens-eda

[category_parent] => 157

[is_post] =>

)

WP_Term Object

(

[term_id] => 159

[name] => Siemens EDA

[slug] => siemens-eda

[term_group] => 0

[term_taxonomy_id] => 159

[taxonomy] => category

[description] =>

[parent] => 157

[count] => 828

[filter] => raw

[cat_ID] => 159

[category_count] => 828

[category_description] =>

[cat_name] => Siemens EDA

[category_nicename] => siemens-eda

[category_parent] => 157

[is_post] =>

)

What does EDA and the Nobel Prize for Physics have in common? Our very own Dr. Walden Rhines (CEO of Mentor Graphics):

The Nobel Prize in Physics 2014 was awarded jointly to Isamu Akasaki, Hiroshi Amano and Shuji Nakamura “for the invention of efficient blue light-emitting diodes which has enabled bright and energy-saving… Read More

We know there is a big divide between analog and digital design methodologies, level of automation, validation and verification processes, yet they cannot stay without each other because any complete system on a chip (SoC) demands them to be together. And therefore, there are different methodologies on the floor to combine analog… Read More

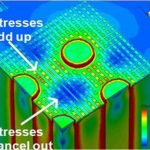

Managing Stress in 3Dby Beth Martin on 09-02-2014 at 1:32 pmCategories: EDA, Siemens EDA

A new publication on mechanical stress in integrated circuits, co-edited by Valeriy Sukharev, Principal Engineer for Calibre R&D at Mentor Graphics, has just been released by AIP Publishing. “Stress-Induced Phenomena and Reliability in 3D Microelectronics” includes 14 key papers from four international workshops … Read More

Mentor’s results came out last week. They were good. Wally opened the call:Thanks. Once again results for Mentor Graphics in the quarter exceeded our guidance. Revenue of $260.2 million and non-GAAP earnings per share of $0.23, were ahead of our guidance of $250 million and $0.15 earnings per share. Strength in bookings… Read More

On Tuesday morning I headed off to the Mentorbooth at DACfor an update on their Custom IC Design and AMS Simulation/Verification tools, Christopher Cone was the presenter. Also in the room were Jay Madiraju, and Mick from Berkeley DA.… Read More

In my career in semiconductor industry, I can recall, in the beginning there was emphasis on design completion with automation as fast as possible. The primary considerations were area and speed of completion of a semiconductor design. Today, with unprecedented increase in multiple functions on the same chip and density of the… Read More

Wally Rhines gave the keynote at DAC in 2004. One of the things that he pointed out ten years ago was that EDA revenue for any given market segment is pretty much flat once the initial growth phase has taken place and the market has been established. Incremental EDA revenue only comes from delivering new capabilities. Historically… Read More

During my illustrious career one of the most useful axioms that I use just about everyday day is: “Understand what people say but also understand why they are saying it.” This certainly applies to press releases so let’s take a look at what Intel unleashed during #51DAC (in alphabetical order):

ANSYS And Intel Collaborate… Read More

For the first time in DAC history there is an automotive track. Being a car person myself this is exciting news. I had a quick chat with Anne Cirkel, Vice Chair of DAC, and she sent me the following information to get us prepared for our week in San Francisco. The weather is going to be great so plan accordingly!

Ever increasing feature… Read More

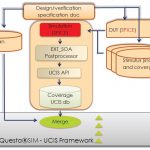

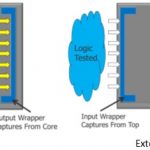

With the advent of large SoCs in semiconductor design space, verification of SoCs has become extremely challenging; no single approach works. And when the size of an SoC can grow to billions of gates, the traditional methods of testability of chips may no longer remain viable considering the needs of large ATPG, memory footprint,… Read More