To fans of Godel, Escher and Bach (the Eternal Golden Braid), there is an appealing self-referential elegance to the idea of verifying a network switch in a cloud-like resource somewhere on the corporate network. That elegance quickly evaporates however when you consider the practical realities of verifying such device in ICE… Read More

The EDAC Wally Rhines Roast (video)

Last week was the EDAC Phil Kaufman award dinner. It was much more like a roast, probably because Wally has a great sense of humor and as Aart de Geus said, “Wally is a cool cat to have a beer with…” Aart is right of course, hanging with Wally is one of my favorite work things to do.

The place was lousy with media people so I will try and add some… Read More

Merger Mania: The Future of the Semiconductor Industry

In a semiconductor industry which appears maturing, we are also seeing the technologies unravelling newer transistor structures, memories, processors, and newer ways of designing ICs and electronic systems. The present decade appears to be at the cusp of a new transformation in the semiconductor industry. Amid a slew of mergers… Read More

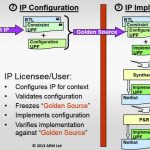

Shifting Low Power Verification to an IP to SoC Flow

One of the most exciting recent developments in low power design and verification is the successive refinement flow developed by ARM® and Mentor Graphics®.… Read More

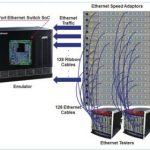

How Virtualization Makes Network Processor Verification Efficient

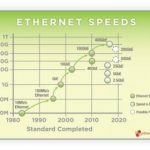

When Ethernet was introduced in 1983 it ran at 10Mbps and mostly relied on hubs and coaxial cable. Twelve years later a faster speed was introduced, running at 100Mbps. Since then we have seen an acceleration of new data rate introductions. According top the Ethernet Alliance, Ethernet could have 12 speeds before 2020, with 6 of … Read More

Price of Admission $0.00 at Inaugural Silicon Valley Conference

Back in 2002, the Southwest DFT Conference was born and experts on design for test (DFT) and test got together to share ideas and talk to people in this industry that were trying to solve test challenges of the day.… Read More

IoT chipsets and enterprise emulation tools

When most people talk about the IoT, it is usually all about wearables-this and low-power-that – because everyone is chasing the next huge consumer post-mobile device market. Mobile devices have provided the model. The smartphone is the on-ramp to the IoT for most consumers, with Bluetooth, Wi-Fi, and LTE, and maybe a dozen or … Read More

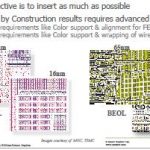

Meeting DFM Challenges with Hierarchical Fill Data Insertion

To describe the latest methodology for the addition of Design for Manufacturability fill shapes to design layout data, it’s appropriate to borrow a song title from Bob Dylan – The Times They Are A Changin’. The new technical requirements are best summarized as: “The goal is now to add as much fill as possible, which (ideally) looks… Read More

Something Old, Something New…EDA and Verification

When I got the opportunity to blog about verification, I thought, what new and interesting things should I talk about? Having started my EDA career in 1983, I often feel like one of the “oldies” in this business…remember when a hard drive required a static strap, held a whopping 33 MB, and was the size of a brick? Perhaps they should … Read More

What’s Testing Design Limits at ITC?

The 46[SUP]th[/SUP] IEEE International Test Conference (ITC) will be held the week of October 5, 2015 at the Disneyland Hotel Conference Center in Anaheim, California. ITC is where you will discover the latest ideas and learn about practical applications of test technologies.

As you take in panels, tutorials, presentations,… Read More