The EDA tool offerings for printed circuit board design commonly address one of three customer markets: (1) the enterprise design team, (2) the product development engineer, and (3) the “maker”. … Read More

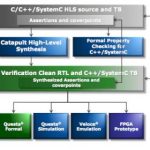

High Level Synthesis Update

High-level synthesis (HLS) involves the generation of an RTL hardware model from a C/C++/SystemC description. The C code is typically referred to as abehavioraloralgorithmicmodel. The C language constructs and semantics available to architects enable efficient and concise coding – the code itself is smaller, easier to write/read,… Read More

ARM and Mentor Enabling the Ecosystem for the Backbone of IoT

Charlene Marini (VP of ARM Segment Marketing) did a nice presentation at the ARM/Mentor Summit last month at the Mentor HQ in Fremont. I just got the slides so let me give you a quick summary from my notes. It was a very good presentation on IoT and emulation which in my mind is the new simulation. I also attended an IoT panel at #53DAC that… Read More

Design for the System Age

Of late, it has become painfully obvious that the value of electronics is in the system. And since systems demand continuing improvement, increasing performance and decreasing cost (once partially guaranteed by semiconductor process advances) is now sought through algorithm advances – witness the Google TPU and custom… Read More

The Evolution of Emulation

Mentor hosted a panel on emulation in their booth at DAC this year. One thing I really liked about this panel is that it didn’t include anyone from Mentor. Not that I have anything against Mentor employees, who are a fine bunch of people from those I know, but I find panels most interesting when the discussion is purely among customers.… Read More

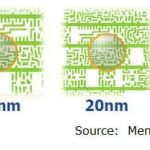

Layout Pattern Matching for DRC, DFM, and Yield Improvement

It is truly amazing to consider the advances in microelectronic process development, using 193i photolithography. The figure below is a stark reminder of the difference between the illuminating wavelength and the final imaged geometries. This technology evolution has been enabled by continued investment in mask data generation… Read More

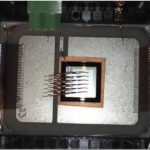

Testing IGBTs before they go into EVs

In the pages of SemiWiki, we are usually talking about what to do with billions of really small transistors – for a change of pace today, we’ll discuss what to do with a few really big ones. Mentor Graphics has just announced their latest MicReD platform for thermal testing of IGBTs, experiencing a resurgence (pun intended) thanks… Read More

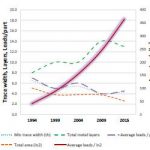

Army of Engineers on Site Only Masks Weakness

Hardware emulation was conceived in the 1980s to address a design verification crisis looming on the horizon. In those days, the largest digital designs were stressing the limits of the software-based, gate-level simulator that was the mainstream tool for the task.

It was anticipated and confirmed in short notice that adopting… Read More

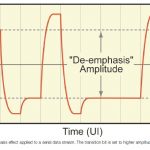

Channel Operating Margin (COM) — A Standard for SI Analysis

There’s an old adage, attributed to renowned computer scientist Andrew Tannenbaum, one that perhaps only engineers find amusing: “The nice thing about standards is that you have so many to choose from.” Nevertheless, IEEE standards arise from customer requirements in the electronics industry. Many relate… Read More

From Simulation to Emulation: 3 Steps to a Portable SystemVerilog/UVM Testbench

If your team is building large, complex designs that require millions of clock cycles to fully verify, you need both simulation and emulation.

Using emulation with simulation accelerates performance for dramatically reduced run times.… Read More