You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 159

[name] => Siemens EDA

[slug] => siemens-eda

[term_group] => 0

[term_taxonomy_id] => 159

[taxonomy] => category

[description] =>

[parent] => 157

[count] => 836

[filter] => raw

[cat_ID] => 159

[category_count] => 836

[category_description] =>

[cat_name] => Siemens EDA

[category_nicename] => siemens-eda

[category_parent] => 157

[is_post] =>

)

WP_Term Object

(

[term_id] => 159

[name] => Siemens EDA

[slug] => siemens-eda

[term_group] => 0

[term_taxonomy_id] => 159

[taxonomy] => category

[description] =>

[parent] => 157

[count] => 836

[filter] => raw

[cat_ID] => 159

[category_count] => 836

[category_description] =>

[cat_name] => Siemens EDA

[category_nicename] => siemens-eda

[category_parent] => 157

[is_post] =>

)

In The Times They Are A Changin’ Nobel Laureate Bob Dylan advised us to “heed the call” of change or suffer the consequences. This couldn’t be more true, considering what design and verification engineers face every day in the midst of the technological revolution.

Change has never been so rapid. And it requires we constantly adapt.… Read More

Last Friday I learned something new about IoT by attending a SEMI event in Wilsonville, OR just a few short miles away from where I live in Tualatin. SEMI puts on two events here in Oregon each year, and their latest event on IoT Sensors was quite timely and popular judging by how many attendees showed up. First up was Jeff Miller from … Read More

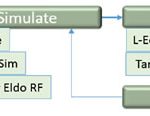

IoT edge device design means four domains – MEMS, analog, digital, and RF – not only work together, but often live on the same die (or substrate in a 2.5D process) and are optimized for power and size. Getting these domains to work together effective calls for an enhanced flow.

Historically, these domains have not played together … Read More

Product lifecycle management is probably not the most gripping topic for most design engineers. You want to get on with architecture, design, verification and implementation. But if you are building products for any safety-sensitive application in a car, a medical appliance, avionics, railway applications in Europe – to name… Read More

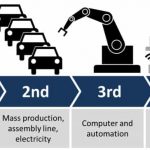

One of the many benefits of blogging is that you get to meet some very interesting people. This time I had the pleasure of speaking with Michael Ford of Mentor Graphics about Industry 4.0 and smart factories. In fact, Mentor has an excellent series of white papers titled “Is This a Manufacturing Revolution?” from their Valor Division,… Read More

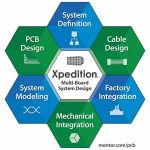

Anybody who has done any bus & board system design knows the problem. Merchant boards typically have standardized pinouts (after years of haggling in standards organizations) for the backplane bus, and a group of user-defined pins for daughtercard I/O. Homegrown systems usually have a just-as-carefully defined proprietary… Read More

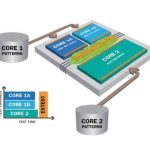

In the early days of IC design there were arguments against using any extra transistors or gates for testability purposes, because that would be adding extra silicon area which in turn would drive up the costs of the chip and product. Today we are older and wiser, realizing that there are product pricing benefits to quickly test each… Read More

The storage market has reached what Andy Grove once described as “…a strategic inflection point.”[1] This is the stage in the life of a business when its fundamentals are about to change.

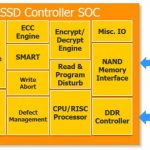

Changing fundamentals in the storage market—where solid state drives (SSD) are now at the forefront of multiple storage applications,… Read More

Next week is ARM TechCon and I’m extra excited about this one because of the SoftBank acquisition. In fact, the opening keynote says it all. ARM CEO Simon Segar and SoftBank CEO Masayoshi Son will discuss the next chapter in the book of ARM. To better prepare for this keynote you should probably read our book “Mobile Unleashed: The … Read More

Low power is now a goal for most digital circuit designs. This is to reduce costs for packaging, cooling, and electricity; to increase battery life; and to improve performance without overheating. I talked to the experts on physical design for ultra-low power at Mentor Graphics recently about the challenges to P&R tools and… Read More