You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 159

[name] => Siemens EDA

[slug] => siemens-eda

[term_group] => 0

[term_taxonomy_id] => 159

[taxonomy] => category

[description] =>

[parent] => 157

[count] => 828

[filter] => raw

[cat_ID] => 159

[category_count] => 828

[category_description] =>

[cat_name] => Siemens EDA

[category_nicename] => siemens-eda

[category_parent] => 157

[is_post] =>

)

WP_Term Object

(

[term_id] => 159

[name] => Siemens EDA

[slug] => siemens-eda

[term_group] => 0

[term_taxonomy_id] => 159

[taxonomy] => category

[description] =>

[parent] => 157

[count] => 828

[filter] => raw

[cat_ID] => 159

[category_count] => 828

[category_description] =>

[cat_name] => Siemens EDA

[category_nicename] => siemens-eda

[category_parent] => 157

[is_post] =>

)

I caught up with John Ferguson of Mentor Graphics this week to learn more about a recent announcement that TSMC has extended its collaboration with Mentor in the area of Fan-Out Wafer Level Processing (FOWLP).

In March of last year Mentor and TSMC announced that they were collaborating on a design and verification flow for TSMC’s… Read More

It’s hard to believe but this is DesignCon #22 and being a Silicon Valley conference I have attended my fair share of them. This year it seems like high speed communications will take the lead followed by the latest on PCB design tools, power and signal integrity, jitter and crosstalk, test and measurement tools, parallel … Read More

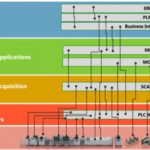

Industry 4.0, Smart Factory 1.0, and Internet of Manufacturing are industry initiatives aimed at accelerating the Industrial IoT. With current market forecast exceeding $40 billion and projected to approach $100 billion by 2020, IIoT has everyone’s attention. Well, almost everyone. Turning volumes of factory data into actionable… Read More

I attended a Mentor verification seminar earlier in the year at which Russ Klein presented a fascinating story about a real customer challenge in debugging a power problem in a design around an ARM cluster. Here’s the story in Russ’ own words. If you’re allergic to marketing stories, read it anyway. You might… Read More

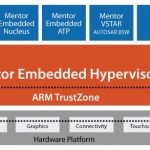

My first exposure to running something virtual on a computer was when I decided to run the Windows OS on my MacBook Pro using software provided by Parallels. With that virtualization I was able to run the Quicken app under Windows on my MacBook Pro, along with the popular Internet Explorer web browser. The app performance on virtualized… Read More

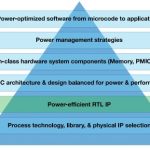

ARM has become such a worldwide powerhouse in delivering processors to the semiconductor IP market because they have done so many things well: IP licensing model, variety, performance, and low-power. On my desk are two devices with ARM IP, a Samsung Galaxy Note 4 smart phone and a Google tablet. Most of my readers will likely have… Read More

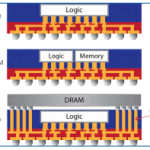

In constant pursuit of improved performance, power and cost, chip and system designers always want to integrate more functions together because this minimizes inter-device loads (affecting performance and power) and bill of materials on the board (affecting cost). However it generally isn’t possible to integrate … Read More

Processor cores come in a wide variety of speeds, performance and capabilities, so it may take you some time to find the proper processor for your system. Let’s say that you are designing a product for the industrial, automotive, military or medical markets that has an inherent requirement for safety, security and reliability… Read More

A few weeks back I wrote an article mentioning that Mentor Graphics has been quietly working on solutions for photonic integrated circuits (PICs) for some time now, while one of their competitors has recently established a photonics beachhead. One of the most common challenges for PIC designs is their curvilinear nature, thus… Read More

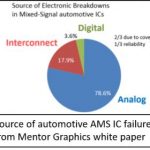

For decades, digital test has been fully automated including methodologies and automation for test pattern generation, grading and test time compression. Automation for analog and mixed-signal (AMS) IC test has not however kept pace. This is troubling as according to IBSapproximately 85% of SoC design starts are now AMS designs.… Read More