Dirk Didascalou, Siemens CTO, gave a keynote at DVCon, raising our perspective on why we do what we do. Yes, our work in semiconductor design enables the cloud and 5G and smart everything, but these technologies push progress for a select few. What about the big global concerns that affect us all: carbon, climate, COVID and conflict?… Read More

Calibre IC Manufacturing papers at SPIE 2023

The Siemens Calibre group was very busy last week at SPIE. Calling Calibre industry leading really is an understatement. Calibre is one of the reasons Moore’s Law has continued to this day. This tool is legendary. You can get more information on the Calibre landing page including product information, resource guide, blogs

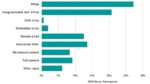

The State of FPGA Functional Verification

Earlier I blogged about IC and ASIC functional verification, so today it’s time to round that out with the state of FPGA functional verification. The Wilson Research Group has been compiling an FPGA report every two years since 2018, so this marks the third time they’ve focused on this design segment. At $5.8 billion… Read More

Interconnect Choices for 2.5D and 3D IC Designs

A quick Google search for “2.5D 3D IC” returns 669,000 results, so it’s a popular topic for the semiconductor industry, and there are plenty of decisions to make, like whether to use an organic substrate or silicon interposer for interconnect of heterogenous semiconductor die. Design teams using 2.5D and … Read More

The State of IC and ASIC Functional Verification

Way back in 2002 there was a study from Collett International Research on functional verification, and since 2010 the Wilson Research Group has continued that same kind of study with a new report every two years. What attracts me to this report is that it doesn’t just look at the installed base of one EDA vendor, instead it looks… Read More

ASIL B Certification on an Industry-Class Root of Trust IP

I have always been curious about how Austemper-based safety methodologies (from Siemens EDA) compares with conventional safety flows. Siemens EDA together with Rambus recently released a white paper on getting a root of trust IP to ASIL B certification. This provides a revealing insight beyond the basics of fault simulation… Read More

3DIC Physical Verification, Siemens EDA and TSMC

At SemiWiki we’ve written four times now about how TSMC is standardizing on a 3DIC physical flow with their approach called 3Dblox, so I watched a presentation from John Ferguson of Siemens EDA to see how their tool flow supports this with the Calibre tools. With a chiplet-based packaging flow there are new physical verification… Read More

Advances in Physical Verification and Thermal Modeling of 3DICs

If, like me, you’ve been paying too little attention to historically less glamorous areas of chip design like packaging, you’ll wake up one day and realize just how much things have changed and continue to advance and how interesting it’s become.

One of the main drivers here is the increasing use of chiplets to counter the decreasing… Read More

Achieving Faster Design Verification Closure

On big chip design projects the logic verification effort can be larger than the design effort, taking up to 70% of the project time based on data from the 2022 Wilson Research Group findings. Sadly, the first silicon success rate has gone downwards from 31 percent to just 24 percent in the past 8 years, causing another spin to correct… Read More

Siemens Aspires to AI in PCB Design

This. AI in PCB design is not a new idea. Other PCB software companies also make that claim. But when a mainstream systems technology company like Siemens talks about the subject, that is noteworthy. They already have an adaptive user interface (UI) for their mechanical modeling suite and to assist in low-code development for application… Read More