In the fast-paced semiconductor industry Synopsys has redefined EDA with its Synopsys.ai Copilot, a generative AI tool. Since its launch in November 2023, and yes I was at the launch and very skeptical, Copilot has evolved to address the industry’s growing design complexity and projected 15-30% workforce gap by 2030. Let’s… Read More

Electronic Design Automation

Webinar Preview – Addressing Functional ECOs for Mixed-Signal ASICs

An engineering change order, or ECO in the context of ASIC design is a way to modify or patch a design after layout without needing to re-implement the design from its starting point. There are many reasons to use an ECO strategy. Some examples include correcting errors that are found in post-synthesis verification, optimizing … Read More

The Rise, Fall, and Rebirth of In-Circuit Emulation (Part 1 of 2)

Introduction: The Historical Roots of Hardware-Assisted Verification

The relentless pace of semiconductor innovation continues to follow an unstoppable trend: the exponential growth of transistor density within a given silicon area. This abundance of available semiconductor fabric has fueled the creativity of design… Read More

Tessent MemoryBIST Expands to Include NVRAM

The concept of built-in self-test for electronics has been around for a while. An article in Electronic Design from 1996 declared that, “built-in self-test (BIST) is nothing new.” The memory subsystem is a particularly large and complex part of any semiconductor design, and it’s one that can be particularly vexing to test. Design… Read More

Smart Verification for Complex UCIe Multi-Die Architectures

By Ujjwal Negi – Siemens EDA

Multi-die architectures are redefining the limits of chip performance and scalability through the integration of multiple dies into a single package to deliver unprecedented computing power, flexibility, and efficiency. At the heart of this transformation is the Universal Chiplet Interconnect… Read More

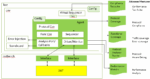

PDF Solutions Adds Security and Scalability to Manufacturing and Test

Everyone knows design complexity is exploding. What used to be difficult is now bordering on impossible. While design and verification challenges occupy a lot of the conversation, the problem is much bigger than this. The new design and manufacturing challenges of 3D innovations and the need to coordinate a much more complex … Read More

Cadence’s Strategic Leap: Acquiring Hexagon’s Design & Engineering Business

In a bold move that underscores the accelerating convergence of electronic design automation (EDA) and mechanical engineering, Cadence Design Systems announced its agreement to acquire Hexagon AB’s Design & Engineering (D&E) business for approximately €2.7 billion, equivalent to about $3.16 billion. This… Read More

WEBINAR: Functional ECO Solution for Mixed-Signal ASIC Design

This webinar, in partnership with Easy-Logic Technology, is to address the complexities and challenges associated with functional ECO (Engineering Change Order) in ASIC design, with a particular focus on mixed-signal designs.

The webinar begins by highlighting the critical role of mixed-signal chips in modern applications,… Read More

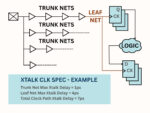

Static Timing Analysis Signoff – A comprehensive and Robust Approach

By Zameer Mohammed

Once a chip is taped out, changes in design are not possible – Silicon is unforgiving, does not allow postproduction modifications. In contrast, software can be updated after release, but chips remain fixed. Static Timing Analysis (STA) signoff serves as a crucial safeguard against silicon failures.

In modern… Read More

eBook on Mastering AI Chip Complexity: Pathways to First-Pass Silicon Success

The rapid evolution of artificial intelligence (AI) is transforming industries, from autonomous vehicles to data centers, demanding unprecedented computational power and efficiency. As highlighted in Synopsys’ guide, the global AI chip market is projected to reach $383 billion by 2032, growing at a 38% CAGR. This … Read More

Quantum Computing Technologies and Challenges