I talked recently with Stelios Diamantidis (Distinguished Architect, Head of Strategy, Autonomous Design Solutions) about Synopsys’ announcement on the 100th customer tapeout using their DSO.ai solution. My concern on AI-related articles is in avoiding the hype that surrounds AI in general, and conversely the skepticism… Read More

Electronic Design Automation

Cliosoft’s Smart Storage Strategy for Better Workspace Management

Over the years storage has gotten very cheap, or has it? As a typical consumer, we take data storage for granted because access to it has gotten very cheap. Long gone are the days of being limited to 1.44MB floppy disks to store data. The smart devices we carry around with us can store 100’s of GB of data. That is a lot of data. But what about… Read More

ASIL B Certification on an Industry-Class Root of Trust IP

I have always been curious about how Austemper-based safety methodologies (from Siemens EDA) compares with conventional safety flows. Siemens EDA together with Rambus recently released a white paper on getting a root of trust IP to ASIL B certification. This provides a revealing insight beyond the basics of fault simulation… Read More

3DIC Physical Verification, Siemens EDA and TSMC

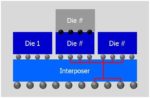

At SemiWiki we’ve written four times now about how TSMC is standardizing on a 3DIC physical flow with their approach called 3Dblox, so I watched a presentation from John Ferguson of Siemens EDA to see how their tool flow supports this with the Calibre tools. With a chiplet-based packaging flow there are new physical verification… Read More

Advances in Physical Verification and Thermal Modeling of 3DICs

If, like me, you’ve been paying too little attention to historically less glamorous areas of chip design like packaging, you’ll wake up one day and realize just how much things have changed and continue to advance and how interesting it’s become.

One of the main drivers here is the increasing use of chiplets to counter the decreasing… Read More

Achieving Faster Design Verification Closure

On big chip design projects the logic verification effort can be larger than the design effort, taking up to 70% of the project time based on data from the 2022 Wilson Research Group findings. Sadly, the first silicon success rate has gone downwards from 31 percent to just 24 percent in the past 8 years, causing another spin to correct… Read More

Podcast EP141: The Role of Synopsys High-Speed SerDes for Future Ethernet Applications

Dan is joined by Priyank Shukla, Staff Product Manager for the Synopsys High Speed SerDes IP portfolio. He has broad experience in analog, mixed-signal design with strong focus on high performance compute, mobile and automotive SoCs and he has a US patent on low power RTC design.

Dan explores the use of high-speed SerDes with Priyank.… Read More

CTO Interview: John R. Cary of Tech-X Corporation

John R. Cary is professor of physics at the University of Colorado at Boulder and CTO of Tech-X Corporation. He received his PhD from the University of California, Berkeley, in Plasma Physics. Prof. Cary worked at Los Alamos National Laboratory and the Institute for Fusion Studies at the University of Texas, Austin, prior to joining… Read More

Designing a ColdADC ASIC For Detecting Neutrinos

Cliosoft recently hosted a webinar where Carl Grace, a scientist from Lawrence Berkeley National Laboratory (LBNL) talked about a cutting edge project for detecting neutrinos. The project is called the Deep Underground Neutrino Experiment (DUNE) project. Many of us know what a neutron is, but what is a neutrino? Before we get… Read More

Webinar: Achieving Consistent RTL Power Accuracy

A comprehensive report from the US Department of Energy (DOE), “Semiconductor Supply Chain Deep Dive Assessment” (February 2022) calls for a 1000X energy efficiency improvement that is required to maintain future compute requirement needs given a finite amount of world energy production. Energy efficiency is at the top of … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center