I haven’t made a secret of the fact that I maintain Oasys Design System’s website. So I had a small task yesterday of adding Qualcomm to the list of customer logos that cycle through on the home page. It is a pretty impressive list including Juniper Networks, Netlogic Microsystems, Texas Instruments and ST Microelectronics.… Read More

Electronic Design Automation

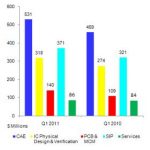

EDA Consortium Newsletter, Q1 2011

Each quarter, the EDA Consortium publishes the Market Statistics Service (MSS) report containing detailed revenue data for the EDA industry. The report compiles data submitted confidentially by both public and private EDA companies into tables and charts listing the data by both EDA category and geographic region. This newsletter… Read More

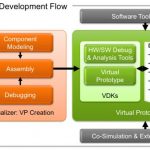

Synopsys Virtualizer

As you probably know, Synopsys last year acquired VaST and CoWare and a couple of years early had acquired Virtio. All three companies primarily competed in the virtual platform market. In addition, Synopsys is the #2 IP company (behind ARM) and has a wide range of tools for SoC design. So the interesting question is how would they… Read More

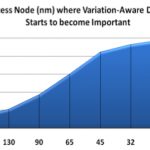

Variation Analysis

I like to say that “you can’t ignore the physics any more” to point out that we have to worry about lots of physical effects that we never needed to consider. But “you can’t ignore the statistics any more” would be another good slogan. In the design world we like to pretend that the world is pass/fail. But manufacturing is actually a statistical… Read More

Richard Goering does Q&A with ClioSoft CEO

Richard Goering is well-known from his editorial days at EE Times (going back some 25 years), now at Cadence he blogs at least once a week on EDA topics that touch Cadence tools.

Before DAC he talked with Srinath Anantharaman about how Cadence tools work together with ClioSoft tools to keep IC Design Data Management Simple.

Through… Read More

Webinar: IP integration methodology

The next Apache webinar is coming up on 21st July at 11am Pacific time on “IP integration methodology”.

This webinar will be conducted by Arvind Shanmugavel, Director Applications Engineering at Apache Design Solutions. Mr. Shanmugavel has been with Apache since 2007, supporting the RedHawk and Totem product … Read More

First low-power webinar: Ultra-low-power Methodology

The first of the low power webinars is coming up on July 19th at 11am Pacific time. The webinar will be conducted by Preeti Gupta, Sr. Technical Marketing Manager at Apache Design Solutions. Preeti has 10 years of experience in the exciting world of CMOS power. She has a Masters in Electrical Engineering from Indian Institute of technology,… Read More

Cadence aquires Azuro

Cadence this morning announced that it has acquired Azuro. Azuro has become a leader in building the clock trees for high performance SoCs. A good rule of thumb is that the clock consumes 30% of the power in an SoC so optimizing it is really important. Terms were not disclosed.

The clock trees involve clock gating which can reduce clock… Read More

Design for test at RTL

Design for test (DFT) imposes various restrictions on the design so that the test automation tools (automatic test pattern approaches such as scan, as well as built-in self-test approaches) will subsequently be able to generate the test program. For example, different test approaches impose constraints on clock generation… Read More

Low Power Webinar Series

At DAC 2011 in San Diego, Apache gave many product presentations. Of course not everyone could make DAC or could make all the presentations in which they were interested. So from mid-July until mid-August these presentations will be given as webinars. Details, and links for registration, are here on the Apache website.

The seminars… Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry