Standards have been proven to reduce cost of operations, drive greater process efficiencies and offer greater opportunities for start-up companies to infuse fresh technology in the design and manufacturing of IC’s. Si2 standards have been targeted to resolve “pinch-points” in the overall semiconductor supply chain… Read More

Electronic Design Automation

Apache Ansys Update 2012

Apache is one of the brightest stars in the EDA universe. Paul McLellan has done a nice job covering them before and after the Ansys acquisition. Check out the Apache SemiWiki landing page HERE. The Apache wikis are also very well done and it has been a pleasure working with the Apache marketing team. Expect more innovative things … Read More

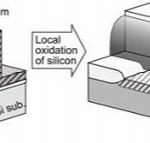

3D Transistors and IC Extraction Tools

Have you ever heard of a Super Pillar Transistor? It’s one of many emerging 3D transistor types, like Intel’s popular FinFET device.

In the race to continuously improve MOS transistors, these new 3D transistor structures pose challenges to the established IC extraction tool flows.

Foundries have to provide an Effective… Read More

Solido Design Automation Update 2012

Having spent a considerable amount of time with Solido, they were one of the founding members of SemiWiki, I can tell you that at 20nm the Variation Designer Platform is a critical part of the emerging 20nm design methodology. You can read more on Solido’s SemiWiki landing page HERE. It is well worth the click.

With technology… Read More

Analog FastSPICE added to Tanner EDA

Last year when I visited Tanner EDA at DAC I heard about how they integrated the Analog FastSPICE circuit simulator from Berkeley DA.

This made sense to me because BDA has a good reputation for speeding up SPICE without compromising on accuracy, and Tanner users may want to mix and match tools from multiple EDA vendors.

This year they’ve… Read More

DAC 2012…need caffeine?

You are in San Francisco for DAC and you want a coffee. OK, if your booth duty is 5 minutes away you pretty much have to take the Moscone coffee. Tastes good, hot, has caffeine. As Meatloaf used to sing (showing my age here) two out of three ain’t bad.

Yes, there are Starbucks all over the city, one on 4th Street just by Moscone Center,… Read More

AMS Programmable Prototype Platforms

AVNET released their 15[SUP]th[/SUP] Xfest this year, a couple of months ago. It was here in Germany last week. It was a well organized event, rich with invaluable technical information and full of decent smart engineers and managers. If you missed it this year register for the next event as soon as you can.

It was a very successful… Read More

EDAC Emerging Companies: Learn How to Emerge

EDAC has a series of seminars for emerging companies with Jim Hogan. Jim has been in EDA since, like, forever. First at National, then at Cadence, then at Artisan (now ARM) and then as an investor first at Telos (Cadence’s VC arm) and more recently on his own at Vista Ventures. He has been involved with many EDA and semiconductor… Read More

Going with the Flow at AMD

At EDPS in Monterey, Tom Spyrou of AMD talked about their compute environment in the context of parallel algorithms. I discovered that they are a big user of RTDA’s FlowTracer so I talked to Philip Steinke at AMD about how they used it.

He said that they largely use it as described in The Art of Flows as a graphical distributed … Read More

Aldec and Tanner EDA at DAC

In April I blogged about a webinar on co-simulation hosted by Aldec and Tanner EDA where they showed how the RTL simulator (Riviera PRO) and SPICE simulator (T-Spice) had been connected together for IC designers wanting to do real AMS simulations.

The availability date of the co-simulation wasn’t clear, so today the press… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era