Breker Verification Systems Plans Demonstrations of its Complete Synthesis and SystemVIP Library and Solutions Portfolio

Attendees who step into the Breker Verification Systems booth during DAC (Booth #2520—second floor) will see demonstrations of its Trek Test Suite Synthesis and SystemVIP libraries and solutions portfolio.… Read More

After being held in San Francisco since the pandemic the beloved Design Automation Conference will be on the move again. In 2026 DAC will be held in Huntington Beach. For you non-California natives, Huntington Beach is a California city Southeast of Los Angeles. It’s known for surf beaches and its long Huntington Beach Pier.… Read More

In this episode of the Semiconductor Insiders video series, Dan is joined by Dr Greg Law, CEO of Undo, He is a C++ debugging expert, well-known conference speaker, and the founder of Undo. Greg explains the history of Undo, initially as a provider of software development and debugging tools for software vendors. He explains that… Read More

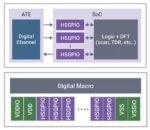

The trend is clear, AI and HPC is moving to chiplet-based, or heterogenous design to achieve the highest levels of performance, while traditional monolithic system-on-chip (SoC) designs struggle to scale. What is also clear is the road to this new design style is not a smooth one. There are many challenges to overcome. Some are … Read More

Another content-rich kickoff covering a lot of bases under three main themes: the new Millennium AI supercomputer release, a moonshot towards full autonomy in chip design exploiting agentic AI, and a growing emphasis on digital twins. Cadence President and CEO Anirudh Devgan touched on what is new today, and also market directions… Read More

Design-Technology Co-Optimization (DTCO) has been a foundational concept in semiconductor engineering for years. So, when Synopsys referenced DTCO in their April 2025 press release about enabling Angstrom-scale chip designs on Intel’s 18A and 18A-P process technologies, it may have sounded familiar—almost expected. … Read More

Intermediate representations (IRs) between high level languages (C++, AI, etc.) and machine language are both commonplace (witness LLVM) and a continuing active area of research. Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO and lecturer at Stanford,… Read More

PCIe is familiar to legions of PC users as a high-performance enabler for expansion slots, especially GPU-based graphics cards and M.2 SSDs. It connects higher-bandwidth networking adapters and niche applications like system expansion chassis in server environments. Each PCIe specification generation has provided a leap… Read More

In this episode of the Semiconductor Insiders video series, Dan is joined by Zackary Glazewski, an ML Engineer at Alpha Design AI. Dan explores the challenges of waveform debugging with Zack, who explains how the process is done today and the shortcoming of existing approaches. He explains why current approaches are time consuming… Read More

Improved profitability and competitiveness are at the very heart of every enterprise. Achievements like this are usually attributed to corporate culture. Sometimes, it’s just being in the right place at the right time. Some organizations make huge investments with top-tier consulting companies to help find their way.

Recently… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center