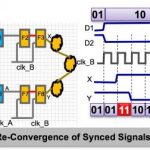

Clock domain crossing (CDC) analysis has been around for many years, initially as special checks in verification or static timing analysis, but it fairly quickly diverged into specialized tools focused just on this problem. CDC checks are important because (a) you can lose data or even lock up at, or downstream of a poorly-handled… Read More

Electronic Design Automation

Evaluating the Performance of Design Data Management Software

In the wake of increased global competitiveness and shorter time-to-market windows, there has been a renewed focus by design management on the underlying data management infrastructure of the design teams. An increasing number of systems-on-chip (SoCs) now have some type of analog, digital and/or RF modules, making it imperative… Read More

The Fine Art of Engineering

There’s a small art gallery near the office. It features a new set of paintings by a local artist every two weeks. As I walk by I tend to check out what’s hanging in there. Sometimes I turn up my nose at what I see – a bit too wacky, a bit too abstract, a bit too paint by numbers. Sometimes I walk in to take a closer look but leave the shop empty-handed… Read More

True Random Number Generation

Random numbers are central to modern security systems. The humble password, perhaps the least profound application, is encrypted and verified against using SHA or MD algorithms with a random number salt. You probably remember a college class on how to generate pseudo-random numbers algorithmically, some very sophisticated.… Read More

Does IoT need Sensor Fusion? Yes, but at low-power, low cost…and higher performance

We said this in the past, but let’s reiterate that IoT devices will be successful if they can meet low-cost and low-power requirements. Low-cost is the condition for IoT devices market penetration, I mean such a market adoption that we count several IoT systems (and dozens of devices) in every house. That’s the only way to reach the… Read More

In Low Voltage Timing, the Center Cannot Hold

When I started discussing this topic with Isadore Katz, I was struggling to find a simple way to explain what he was telling me – that delay and variance calculations in STA tools are wrong at low voltage because the average (the center) of a timing distribution shifts from where you think it is going to be. He told me that I’m not alone… Read More

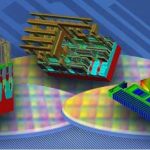

The Death of Moore’s Law

For the last several years, people have predicted the end of Moore’s Law. The reasoning is that there is a limit at which one can’t shrink transistors any further. A reoccurring comment has been “You can’t divide an atom.” I had assumed that its demise would be at the hands of a new paradigm like quantum computing. Now, with Intel’s … Read More

When Good Standards Get Lost – the UVM Register Model

Some time ago I wrote a DeepChip viewpoint on DVCON 2014 in which I praised a Mentor paper “Of Camels and Committees”. The authors argued that while the UVM standards committee had a done a great job in the early releases, the 1.2 release was overloaded with nice-to-have features with questionable value for a standard, particularly… Read More

Coventor ASML IMEC: The last half nanometer

On Tuesday evening December 8[SUP]th[/SUP] at IEDM, Coventor held a panel discussion entitled the “The last half nanometer”. Coventor is a leading provider of simulation software used to design processes. This is my third year attending the Coventor panel discussion at IEDM and they are always excellent with very strong panels… Read More

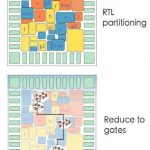

Decisive Floorplanning for Faster Design Closure

Semiconductor design automation at system level is gaining its due importance today. It needs an effective, efficient, and seamless flow from system up to silicon. There is lot of effort going on for automating SoC design exploration at system level but that eventually stops at RTL; another level of flow automation takes over … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center