Formal verification for hardware was stuck for a long time with a reputation of being interesting but difficult to use and consequently limited to niche applications. Jasper worked hard to change this, particularly with their apps for JasperGold and I have been seeing more anecdotal information that mainstream adoption is growing.… Read More

Electronic Design Automation

IMEC Technology Forum at SEMICON – Coventor could save you billions!

The development of leading edge semiconductor technology is incredibly expensive, with estimates ranging from a few to several billion dollars for new nodes. The time to develop a leading edge process is also a critical competitive issue with some of the largest opportunities awarded based on who is first to yield on a new node.… Read More

10nm Will Be an Epic Process Node!

In the history of the fabless semiconductor industry the foundries have always been a process node or two behind the leading semiconductor manufacturers. Starting in Q1 2017, for the first time in fabless semiconductor history, the foundries will have a process node advantage. This is horrible news for some but great news for … Read More

Can one process handle IIoT safety and security?

SemiWiki had another article recently making the case that in IoT applications, safety and security are intertwined, adding that both are important, but they are not the same thing. Mentor Graphics has weighed in with a new white paper trying to tie both issues to a methodology.

Industrial IoT – or IIoT as you’ll often see in shorthand… Read More

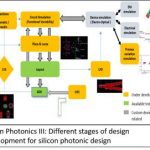

Electrical-Optical Design, A Bridge to Terabitsia

If you don’t get the tongue in cheek reference of the title, you probably don’t have children who liked to watch Disney movies. All four of my daughters loved Disney and so, I am forever shaped by the Wonderful World of Disney. In 2007 Disney adapted to the screen a novel called, ‘A Bridge to Terabithia’, in which two adolescents escape… Read More

10 Challenges in IP Design Collaboration

Enterprise design management can be summed up in one word: collaboration. Intellectual property (IP) reuse and the success of distributed system-on-chip (SoC) design efforts depend strongly on how well designers can collaborate. As time-to-market windows have shortened, the challenges around design collaboration have… Read More

Integrity and Reliability in Analog and Mixed-Signal

In the largest and fastest growing categories in electronics – mobile, IoT and automotive – analog is playing an increasingly important role. It’s important in delivering high integrity power and critical signals to the design though LDO regulators and PLLs, in managing high speed interfaces like DDR and SERDES, in interfacing… Read More

New Transistor Sizing Company at #53DAC

I first met Herve Guegan at Mentor Graphics back in the late 90’s when he managed a group of developers for the SPICE circuit simulator called Eldo in Grenoble, France. We’ve kept in touch over the years and he asked to meet me at DAC in Austin this year, so I caught up with him to get an update on his latest start-up company… Read More

IC and System Design for Mobile and Wearable Devices!

The Linley Mobile and Wearable Conference is coming up so let’s take a look at what is in store for us. Bernard Murphy, Tom Simon, and I will be covering the event live for SemiWiki and we will also be doing a book giveaway/signing for our new “Prototypical” book (compliments of S2C Inc.) during the networking event on Tuesday evening.… Read More

Webinar alert – Hybrid prototyping for ARMv8

All the talk about ARM server SoCs has been focused on who will come up with the breakthrough chip design. Watching trends like OPNFV develop suggests the big breakthrough is more likely to come on the ARMv8 software side. How do you quickly validate ARMv8 software when you don’t have the exact ARMv8 SoC target?… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center