It’s always a pleasure when a vendor gives a really informative, vendor-independent presentation on what’s happening in some domain of the industry and wraps up with (by that point) a well-deserved summary of that vendor’ solutions in that space. Ron Lowman did just that at the Linley conference on Mobile and Wearables, where … Read More

Electronic Design Automation

Why using new DDR4 allow designing incredibly more efficient Server/Storage applications?

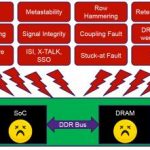

The old one-size-fits-all approach doesn’t work anymore for DDR4 memory controller IP, especially when addressing the enterprise segments, or application like servers, storage and networking. For mobile or high end consumer segments, we can easily identify two key factors: price (memory amount or controller footprint) … Read More

At What Point Does Transistor Gate Length Stop Getting Smaller?

When I started doing IC design back in 1978 we had 6,000 nm channel gate lengths, and today you can buy a smart phone with 16 nm or 14 nm technology, although the gate lengths in those phones are more like 34 nm. The International Technology Roadmap for Semiconductors (ITRS) makes predictions about emerging trends in our industry and… Read More

A Credible Player at the Power Table

For a while it seemed like Mentor lived on the margins of the (RTL) design-for-power game. They had interesting micro-architectural optimization capabilities through their Calypto heritage but no real industry chops in power estimation, a must-have when you are claiming to reduce power. Better known offerings in RTL power … Read More

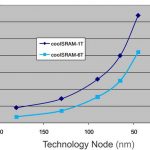

1-T SRAMs in high-density, portable applications

For SoCs designed for various applications such as mobile, automotive, wearable computing, gaming, virtual reality, PC, imaging, security, and IOT applications, it is incredibly important to keep area (cost) and power as low as possible. Considering the growing percentage of chip area used for memory, it makes sense to choose… Read More

AMD Unveils Full Radeon RX 400 Models And Positioning At E3

At E3 2016 in Los Angeles, California Advanced Micro Devices disclosed the numbering and targeted use cases of their full line of Polaris-based GPUs, branded as the “Radeon RX Series” of graphics cards. Advanced Micro Devices had previously disclosed some details about the new Radeon RX series of graphics cards at Computex 2016… Read More

NVIDIA Rounds Out Pascal-Based GeForce Lineup With GTX 1060 And New Software Features

NVIDIA has been working hard to progress forward their new Pascal family of GPUs ever since their announcement at Dreamhack in May 2016 in my hometown, Austin, TX. The announcement included two of NVIDIA’s newest GPUs, the GTX 1080 and GTX 1070, both of which are somewhat available now. I worked with my colleague, Anshel Sag, to review… Read More

Why is AMD Stock Jumping?

One of my favorite pastimes is listening to the quarterly investor calls of the leading semiconductor companies. I can then match up the talking points with the calls I do with Wall Street, the conferences I attend, and the other data points I have collected while working inside the fabless semiconductor ecosystem for more than … Read More

Dragging RTL Creation into the 21st Century

When I was at Atrenta, we always thought it would be great to do as-you-type RTL linting. It’s the natural use model for anyone used to writing text in virtually any modern application (especially on the Web, thanks to Google spell and grammar-checks). You may argue that you create your RTL in Vi or EMACS and you don’t need no stinking… Read More

The Appeal of a Multi-Purpose DSP

When you think of a DSP IP, you tend to think of very targeted applications – for baseband signal processing or audio or vision perhaps. Whatever the application, sometimes you want a solution optimally tuned to that need: best possible performance and power in the smallest possible footprint. These needs will continue,… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center