One of the important changes that happen between 1984 and 1988 is the hardware platforms development. Calma evolved, mainframe S140 with 2 combined monitors per terminal in S280 with 2 individual monitors per terminal. This meant that from noisy and darker rooms we move to more quiet and lighted rooms. We doubled the speed and the… Read More

Electronic Design Automation

Photonics Summit Delivers High-Bandwidth Discussion on State of Silicon Photonics

On September 6, 2017, Cadence Design Systems, Lumerical Solutions and PhoeniX Software hosted their second Photonics Summit. As with last year’s summit, this was a two-day event, with the first day including in a myriad of photonics presentations and the second day being a hands-on workshop. The hands-on workshop taught attendees… Read More

Adoption, Architecture and Origami

Last week I sat in on Oski’s latest in a series of “Decoding Formal” sessions. Judging by my first experience, they plan and manage these events very well. Not too long (~3 hours of talks), good food (DishDash), good customer content, a good forward-looking topic and a very entertaining wrap-up talk.… Read More

TSMC Teamwork Translates to Technical Triumph

Most people think that designing successful high speed analog circuits requires a mixture of magic, skill and lots of hard work. While this might be true, in reality it also requires a large dose of collaboration among each of the members of the design, tool and fabrication panoply. This point was recently made abundantly clear … Read More

Design for Manufacturability Analysis for PCB’s

Chip designers are familiar with the additional physical design checking requirements that were incorporated into flows at advanced process nodes. With the introduction of optical correction and inverse lithography technology applied during mask data generation, and with the extension of a 193nm exposure source to finer… Read More

Emulation Methodology for Drones and Other Video-Intensive Multimedia SoCs

What do drones, augmented reality devices, and 4K UHD TV have in common? They all include complex system-on-chips (SoCs) that must encode and decode, in real-time, data for increasingly higher definition video content. Verifying that these SoC designs are functionally correct is quite complex, but they must also function efficiently… Read More

High-Speed Equivalence Checking

Following on product introductions for simulation and prototyping, physical verification and implementation earlier in the year, Anirudh Devgan (Exec VP and GM at Cadence), the king of speed and parallelism has done it again, this time with logic equivalence checking (LEC). Cadence recently announced an advance to their well-known… Read More

Portable Stimulus Standard, What’s New from Cadence

I’ve been hearing about the Portable Stimulus Standard (PSS) since DAC 2016, so it’s helpful to get an update from EDA vendors on what their involvement level is with this emerging standard and how they see it helping design and verification engineers. Earlier in September I scheduled a conference call with Cadence… Read More

CDNLive Boston Keynote Address Highlights Emergence of Silicon Photonics

I had the pleasure of being able to attend the CDNLive event held in the Boston, MA area last month and I was pleasantly surprised to see that Cadence highlighted Silicon Photonics as one of its Keynote topics. MIT Professor Duane Boning gave an excellent overview of the current state of silicon photonics and why he believes it is time… Read More

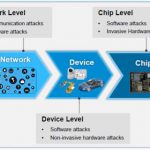

How to Avoid Jeopardizing SoC Security when Implementing eSIM?

Smart card business is now more than 25 years old, we can assess that the semiconductor industry is able to protect the chips used for smart card or SIM application with a very good level (unfortunately, it’s very difficult to get access to the fraud percentage linked with smart cards, as bankers really don’t like to communicate on… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center