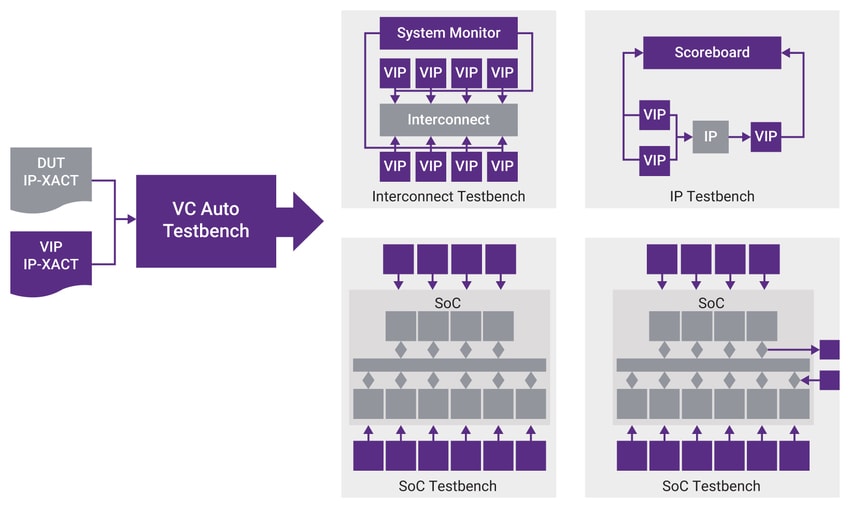

There seems to be a general sense that we have the foundations for block/IP verification more or less under control, thanks to UVM standardizing infrastructure for directed and constrained-random testing, along with class libraries providing building blocks to simplify verification reuse, build sequence tests, verify register… Read More

Electronic Design Automation

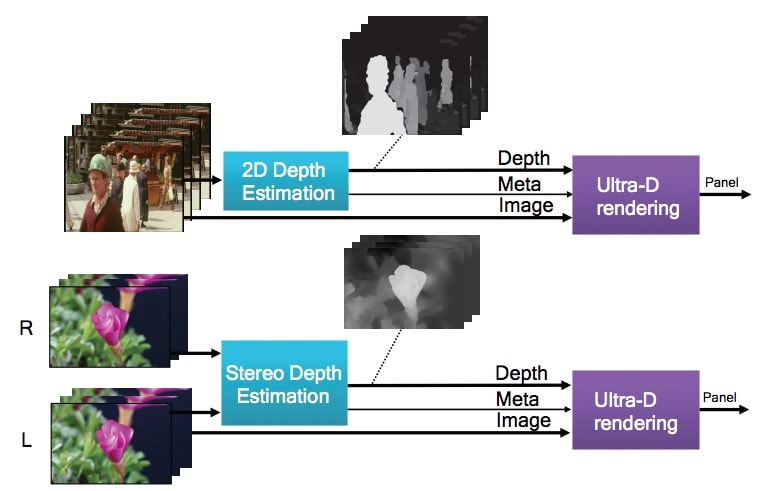

Designing an SoC for 3D TV Without using the Funny Glasses

In the blur of activities at DAC last year I visited the Mentor booth a few times and had just a few minutes to glance at a 3D TV display that didn’t require me to wear any funny glasses, kind of novel I thought at the time because I’ve read that the market of 3D TV sets is being hampered by requiring viewers to wear glasses. The… Read More

Simulation and Formal – Finding the Right Balance

Simulation dominates hardware functional verification today and likely will continue to dominate for the foreseeable future. Meanwhile formal verification, once thought to be a possible challenger for the title, has instead converged on a more effective role as a complement to simulation. Formal excels at finding problems… Read More

Moore’s Law Drives Foundries and IP Providers

2017 was a banner year for semiconductor sales as they topped $400B for the first time, an increase of some 20%, there is happiness in Silicon Valley, Taiwan, South Korea, and well, everywhere. With the foundries pushing to ever-smaller process dimensions and even going back to mature nodes and offering more variations that are… Read More

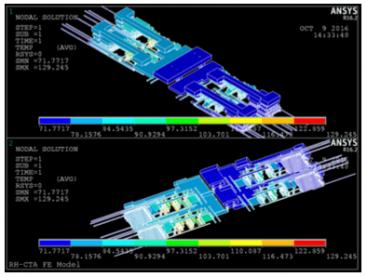

Thermal Modeling for ADAS goes MultiPhysics

In electronic system design, we have grown comfortable with the idea that different regimes of analysis, such as the chip, the package and the system, or electrical, thermal and stress are more or less independent – what starts in one regime stays in that regime, give or take some margin information passed onto other regimes. And… Read More

A Reliable Way to Forecast Growth of Semiconductor Markets

Wally Rhines, President and CEO of Mentor, a Siemens Group, did another one of his famous deep learning presentations at SEMI ISS 2018. Using the Gompertz Curve Lifecycle to forecast the future growth of semiconductor markets, Wally looks at: Image sensors, Desktop PCs, PC Notebooks, Cell Phone Subscribers, Smartphones, and… Read More

Mentor Tessent Products Ready for Second Edition of ISO 26262 Coming in March 2018

Have you notice how smart your automobile is getting? Watching the first round of NFL playoffs I lost count on the number of TV commercials showing cars weaving through tight construction zones (and Star Wars figures), big trucks parking in incredibly tight spaces, cars avoiding rear-end collisions and pedestrians, and even … Read More

Scoreboard and Issues Management Tools for PCB Projects

The complexity of an SoC design necessitates that the project managers have accurate visibility into the overall design status, spanning the entire range of tasks – from functional simulation error triage, to physical layout verification errors, to electrical analysis results. Flow scripts used by SoC teams parse the log file… Read More

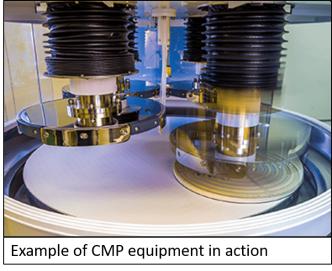

Mentor Investigates Using Neural Networks for CMP Modeling

I recently read a new white paper release by Mentor, a Siemens Business, that delved into the intricacies of Chemical Mechanical Polishing (CMP) and I got a sense of Déjà vu. My professional career in the IC industry started at Texas instruments and the white paper made me think of a conversation I had with one of my colleagues over … Read More

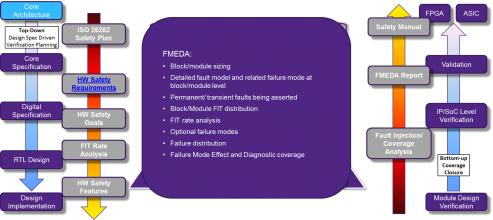

Achieving ISO 26262 Certification with ASIL Ready IP

According with McKinsey, “analysts predict revenue growth for advanced driver assistance systems (ADAS) to be up to 29 percent, giving the segment one of the highest growth rates in the automotive and related industries.” Design cycle in automotive segment is much longer than in segments like mobile, PC or consumer. If you expect… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center