Lurking inside of every Mosfet is a parasitic bipolar junction transistor (BJT). Of course, in normal circuit operation the BJT does not play a role in the device operation. Accordingly, SPICE models for Mosfets do not behave well when the BJT is triggered. However, these models work just fine for most purposes. The one important… Read More

Electronic Design Automation

Siemens Shows SOC Simulation Solution for Self-Driving Vehicles

Ever since the early days of computing there has always been a large distinction between ‘regular’ computing and real time computing – where special care had to be made to deal with unordered and asynchronous events. Back then a system typically consisted of a handful of sensors and perhaps some electromechanical devices.… Read More

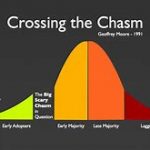

Tortuga Crosses a Chasm

I assume you know the Geoffrey Moore “crossing the chasm” concept, jumping from early stage enthusiasts trying your product because they’ll try anything new, to expanding to a mainstream and intrinsically more critical audience – a much tougher proposition. I’d argue there may be more than one of these transitions in the… Read More

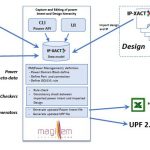

Magillem offers a practical UPF power flow

We already know that IP-Xact is extremely useful for managing IP and SOC design specifications, yet it may come as a surprise to learn that it also can be used to form the basis of a power flow too. There are design tools that read UPF to help implement and verify designs, however it can be extremely useful to understand the interplay … Read More

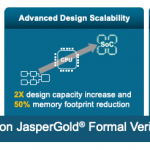

JasperGold Gets Smarter, Faster and Easier for Signoff

Machine learning (ML) is already making its way into EDA tools and flows, but the majority of announcements have been around implementation, especially in guiding toward improved timing and area. This is a pretty obvious place to start; ML is in one sense an optimization technique, trained on prior examples, which should be able… Read More

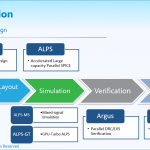

56th DAC Empyrean Stepping Up ALPS with GPU Implementation

As a testament to the technology advances developed and implemented into Empyrean ALPS™ by the engineering team, the product has seen a steady growth in the adoption by users. In addition, hearing directly from the users at DAC 2018 turned out to be an all-around success for the product as well as the product team to see ALPS beating… Read More

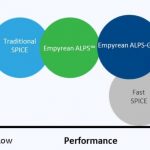

The Changing Landscape for SPICE Circuit Simulators

I first started using a SPICE circuit simulator in 1978 while at Intel and have followed that market ever since then. Back at DAC in 2012 I first heard of a Chinese EDA company called IC Scape with a SPICE circuit simulator called Aeolus, so I blogged about it. Fast forward to 2019 and I heard from Ravi Ravikumar, a former co-worker from… Read More

Automotive Design and Virtual Prototyping

The entire history of EDA software tools has enabled engineers to design ICs and SoCs using virtual prototyping, so most of us in the industry are familiar with the idea of modeling and simulating something as complex as an IC before actually starting the manufacturing process. In a complex system like an automobile there are a lot… Read More

Mentor Excitement at 56thDAC!

Mentor continues to invest in conferences such as DAC, no matter the location, for which I am very grateful. They have a long list of activities this year but I wanted to point out my top three:

Wally Rhines has a talk in the DAC Pavilion which is first on the list. Wally’s expert industry perspective is the result of tireless research… Read More

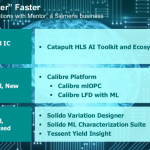

Mentor Extends AI Footprint

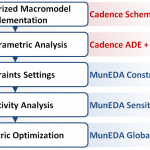

Mentor are stepping up their game in AI/ML. They already had a well-established start through the Solido acquisition in Variation Designer and the ML Characterization Suite, and through Tessent Yield Insight. They have also made progress in prior releases towards supporting design for ML accelerators using Catapult HLS. Now… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era