Defacto SoC Compiler whose 9.0 release was announced recently automates the SoC design creation from the first project specifications. It covers register handling, IP and connectivity insertion at RTL, UPF and SDC file generation right to logic synthesis. As part of the generation process of RTL and design collaterals, basic… Read More

Electronic Design Automation

CEO Interview: Toshio Nakama of S2C EDA

Toshio Nakama is the founder and the CEO of S2C and also a strong advocate of FPGA accelerated ASIC/SoC design methodology. Mr. Nakama devotes much of his time in promoting scalable Prototyping/Emulation hardware architecture and defining automated software specifications. He first started his career at Altera in 1997 and … Read More

Upping the Safety Game Plan for Automotive SoCs

Thanks to advanced hardware and software, smart vehicles are improving with every generation. Capabilities that once seemed far-off and futuristic—from automatic braking to self-driving at the very pinnacle—are now either standard or within reach. However, considering how vehicle architectures have continued to evolve,… Read More

Chip Design in the Cloud – Annapurna Labs and Altair

The above title refers to a webinar that was hosted by Altair on April 28th. Chip design in the cloud is not a new idea. So, what is the big deal with the above title. Sometimes titles don’t reveal the full story. Annapurna Labs happens to be an Amazon company. It used to be an independent semiconductor company that was acquired by Amazon… Read More

The Quest for Bugs: Bugs of Power

Shooting beyond the hill…

In former times (think WW1 before GPS and satellites), an artillery battery trying to shell targets out of sight behind a hill would have to rely on an approximate grid reference and a couple of soldiers on top of the hill (who could see the target) to tell them where the shots were landing. These range finders… Read More

COO Interview: Michiel Ligthart of Verific

Today, Semiwiki profiles Verific Design Automation, perhaps the most popular company at DAC (when it’s an in-person event) because of its giveaway –– a 10”stuffed giraffe for anyone who walks up to its booth and listens to its story.

But, Verific is also a popular EDA company for more reasons than its tradeshow giveaway.… Read More

Your IP Portfolio is Probably Leaking. What Can You Do About It?

This topic is inspired by a presentation at last year’s DAC presented by Methodics, now part of Perforce. The issues raised by the original presentation are still quite relevant in the current business climate. IP leakage is something everyone should consider as part of their normal business operations. Your design IP really … Read More

Developing Verification Flows for Silicon Photonics

Silicon photonics is getting a lot of interest because it can be used in many applications to improve bandwidth, reduce power and provide novel new functionality. It is especially interesting because it offers an ability to combine electronics and optical elements into the same die. Though it is fabricated with familiar silicon… Read More

Formal Verification Approach Continues to Grow

After a few decades of watching formal verification techniques being applied to SoC designs, it certainly continues to be a growth market for EDA vendors. In the first decades from 1970-1990 the earliest forms of formal tools emerged at technical conferences, typically written by University students earning their Ph.D.s, … Read More

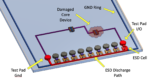

Magwel Adds Core Device Checking for ESD Verification

In the past ESD sign-off has been accomplished by a combination of techniques. Often ESD experts are asked to look at a design and assess its ESD robustness based on experience gained from prior chips. Alternatively, designers are told to work with a set of rules given to them, again based on previous experience about what usually… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era