At times it has seemed like any development in EDA had to build a GenAI app that would catch the attention of Wall Street. Now I see more attention to GenAI being used for less glamorous but eminently more practical advances. This recent white paper from Siemens on how to help verification engineers get up to speed faster with PSS is … Read More

Electronic Design Automation

Accelerating NPI with Deep Data: From First Silicon to Volume

For decades, semiconductor teams have relied on traditional methods such as corner-based analysis, surrogate monitors, and population-level statistical screening for post-silicon validation. These methods served well when variability was modest, and timing paths behaved predictably. However, today’s advanced nodes… Read More

We Need to Turn Specs into Oracles for Agentic Verification

The natural language understanding now possible in LLMs has raised interest in using specs as a direct reference for test generation, to eliminate need for intermediate and fallible human translation. Sadly, specs today are not an infallible source of truth for multiple reasons. I am grateful to Shelly Henry (CEO of MooresLab)… Read More

Accelerating SRAM Design Cycles: MediaTek’s Adoption of Siemens EDA’s Additive AI Technology at TSMC OIP 2025

In the competitive vertical of mobile System-on-Chip development, SRAM plays a pivotal role, occupying nearly 40% of chip area and directly impacting yield and performance. The presentation “Accelerating SRAM Design Cycles With Additive AI Technology,” co-delivered by Mohamed Atoua of Siemens EDA and Deepesh… Read More

Transforming Functional Verification through Intelligence

SoC projects are running behind schedule as design and verification complexity has increased dramatically, so just adding more engineers, more tests and more compute aren’t the answer. The time is ripe to consider smarter ways to improve verification efficiency. The added complexity of multiple embedded processors, multiple… Read More

WEBINAR: Revolutionizing Electrical Verification in IC Design

In the complex world of IC design, electrical verification has emerged as a critical yet often overlooked bottleneck. Aniah’s upcoming webinar on December 4, 2025, titled “Electrical Verification: The Invisible Bottleneck in IC Design,” sheds light on this issue, introducing their groundbreaking OneCheck® solution. … Read More

From Silos to Systems, From Data to Insight: Keysight’s Upcoming Webinar on EDA Data Transformation

In the fast-evolving world of electronic design automation (EDA), where complexity multiplies with every nanometer shrink and AI integration, data silos are the silent killers of innovation. Keysight Technologies, a leader in design and test solutions, tackles this head-on with their webinar “From Silos to Systems,… Read More

Agentic Bug Localization. Innovation in Verification

Bug localization continues to be a challenge for both bug triage and root-cause analysis. Agentic approaches suggest a way forward. Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO and lecturer at Stanford, EE292A) and I continue our series on research ideas.… Read More

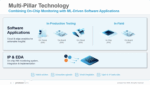

Why chip design needs industrial-grade EDA AI

By Niranjan Sitapure

Artificial intelligence (AI) is reshaping industries worldwide. Consumer-grade AI solutions are getting significant attention in the media for their creativity, speed, and accessibility—from ChatGPT and Meta’s AI app to Gemini for image creation, Sora for video, Sona for music, and Perplexity for web… Read More

Cloud-Accelerated EDA Development

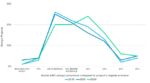

By Nikhil Sharma, Sunghwan Son, Paul Mantey

The semiconductor industry faces an unprecedented crisis that threatens the very foundation of technological innovation. According to the latest Siemens EDA / Wilson Research Study, first-silicon success rates have plummeted to just 14%[1]—the lowest figure in more than twenty… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era