Publishing eBooks on FPGA Prototyping and Emulation really was an eye opener for me as a long time EDA and IP professional. Both markets are considered EDA in the traditional sense but they are very much in the systems business with a lot of IP. Both markets are also growing very rapidly and operate side-by-side with complimentary overlap. Emulation of course is a billion dollar prize in the making with AI rapidly consuming silicon and increasing die sizes in all market segments, absolutely.

Last week we had a call with Mentor to talk to Jean-Marie Brunet, Senior Director of Marketing at Mentor Graphics, a Siemens Business (Jean-Marie is the one who sponsored our book on SoC Emulation). Today Mentor is announcing expansions to the Veloce Strato Emulation Platform which represents several industry firsts.

Here are my notes on the call and follow-on email:

– Emulation market growing rapidly, as the functional validation coverage for even moderate-sized SoC’s are more demanding for all applications.

– ISO 26262 for automotive applications requires a detailed assessment of the testing of embedded software. For example, there is a risk that unintended functionality is present in the code generator and that, under some circumstances that would not be detected by requirements-based test cases of the code generator, this would lead to a catastrophic failure of the embedded software. This is precisely the role of a typical safety process such as ISO 26262.

– The Veloce emulator incorporates a unique programmable logic architecture, based on a custom chip design developed by Mentor. This design differs from a commercial FPGA, providing improved internal signal tracing (traditionally, an issue with other FPGA-based emulators).

– StratoT: Mentor is announcing a lower “cost-of-entry” emulation product offering.

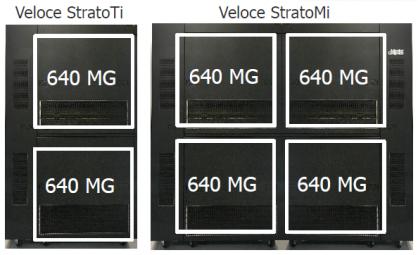

– A Veloce system consists of emulation modules, each with capacity up to 640M gates. To save $$$, Mentor is offering an “independent” system architecture, reducing the complexity of the backplane switch in the chassis (see figure).

– For customers who can fit one (or more) models into the module, this simplified architecture offers a cost reduction.

– Last year Mentor announced the industry’s first emulation solution with a path to 15B gates. A year later, Mentor is clearly executing effectively and making good on this bold statement:

– In the year since introduction, no competitor has followed up Mentor’s plans for roadmap to 15BG, (hence, Veloce Strato is still highest capacity emulation tech in the industry).

– Today, Mentor introduces StratoT, which demonstrates the Strato family’s scalability, and “completing the story” regarding chassis footprint options for Strato. Veloce can scale to >2.5 Bgates via deploying multiple StratoM boxes.

– Mentor has secured several customers for Strato products, including Samsung, who proclaim that Strato has transformed “shift left” from a marketing term to a reality for Samsung. More customers to be announced in quarters ahead.

– Customer feedback upon deploying Strato: customers report to us that power efficiency is 30% better than we estimated and communicated at launch/introduction–this reinforces the cost-of-ownership advantages of Strato.

– In addition to silicon emulation, Veloce is now #1 in other markets including networking, multimedia, mobile, and CPU.

– Since Strato launch a year ago, Siemens has proven to be a key competitive differentiator, since Siemens is investing in emulation leadership for Mentor. The recent Mentor acquisition of Sarokal serves as strong evidence of Siemens’ investment commitment in the investment-heavy emulation space.

– Siemens is a global leader in “digital twin” technology, and Veloce is the centerpiece for Siemens automotive digital twin plans. Supporting data point: Mentor recently announced that Infineon is using Veloce.

In our SoC Emulation book there is a nice landscape of the business. Here are the contents of the first half in case you are interested:

Introduction – Why Emulation 1

Verification and Validation 2

The Performance Wall for Simulation 3

The Beginnings of Emulation in Hardware Design 5

Chapter 1 – ICE is Nice 7

Arrays of FPGAs 8

The Good, the Bad and the Not So Bad 10

Emulation Versus FPGA Prototyping 12

Chapter 2 – Three Architectures 14

Processor-Based Emulation 15

Emulation Based on Custom FPGAs 17

Emulation Based on Commercial FPGAs 20

Timing in the Three Architectures 22

Chapter 3 – Emulation Muscles onto Simulation Turf 24

Speeding Up the Test Environment 24

Multi-User Support 26

A Change in Approach to Debug 29

Chapter 4 – Accelerating Software-Based Verification 31

The Rise of Software in Electronics 31

Why Software is Important in Verification 32

Emulation and Hardware/Software Co-verification 33

All Software isn’t Equally Important to V&V 34

Debugging in Hardware/Software Co-verification 35

Chapter 5 – Beyond Traditional Verification 36

Performance Modeling 36

Power Modeling 36

Test Verification 37

Deterministic ICE 38

Complex Load Modeling 39

Chapter 6 – The Role of Emulation in Design Today 40

Virtual Prototyping and Emulation 40

Simulation and Emulation 41

Emulation and FPGA Prototyping 44

The Outlook for Emulation 45

Comments

There are no comments yet.

You must register or log in to view/post comments.