Although semiconductor community has ushered into the era of SoCs, the verification of SoCs is still broken. There is no single methodology or engine to verify a complete SoC; this results in duplication of efforts and resources for test creation and verification at multiple stages in the SoC development, albeit with different… Read More

Author: Pawan Fangaria

Reusable HW/SW Interface for Portable Stimulus

DRC Concept for IP Qualification and SoC Integration

In the history of semiconductor design and manufacturing, the age-old concept of DRC rule-deck qualification for handshake between design and manufacturing still applies strongly to produce working silicon. In fact, DRC clean GDSII works as the de facto golden gate between a design and a foundry for manufacturing the chip for… Read More

How TSMC Tackles Variation at Advanced Nodes

The design community is always hungry for high-performance, low-power, and low-cost devices. There is emergence of FinFET and FDSOI technologies at ultra-low process nodes to provide high-performance and low-power requirements at lower die-size. However, these advanced process nodes are prone to new sources of variation.… Read More

CEO Insight: Transformation of Vayavya Labs into System Design Automation

With the advent of SoCs, design abstractions and verification has moved up at the system level. It’s imperative that EDA moves up the value chain to start design automation at system level. The System Design Automation will be the new face of EDA in coming years.… Read More

IoT Devices Making Inroads into Semicon Revenue

Last year IC Insights forecasted IOT semiconductor growth rate to be around 19% CAGR for next five years. And within that space, the O-S-D (Optoelectronics, Sensors, and Discrete) semiconductors were expected to grow at a CAGR of 26%, one among the fastest. In 2015, the O-S-D revenue was at $66.6 billion, i.e. ~19% of total semiconductor… Read More

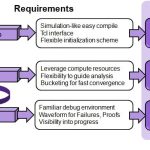

Bringing Formal Verification into Mainstream

Formal verification can provide a large productivity gain in discovering, analyzing, and debugging complex problems buried deep in a design, which may be suspected but not clearly visible or identifiable by other verification methods. However, use of formal verification methods hasn’t been common due to its perceived complexity… Read More

The Semicon Industry Keeps Wafer Fabs Moving Up

The worldwide revenue of semiconductor industry has remained flat in last few years; to be more precise, overall semiconductor revenue declined by 1.9% in 2015 and Gartner forecasts it to further decline by 0.6% in 2016. The total revenue was at record high of $340.3 billion in 2014.

Well, semiconductor industry has matured. A … Read More

A Versatile Design Platform with Multi-Language APIs

In one of my whitepapers “SoCs in New Context – Look beyond PPA”, I had mentioned about several considerations which have become very important in addition to power, performance, and area (PPA) of an SoC. This whitepaper was also posted in parts as blogs on Semiwiki (links are mentioned below). Two important… Read More

How China can Lead in the Semiconductor Industry

Since a few years China has been very aggressive in acquiring semiconductor companies around the world. Last year, Chinese government along with PE (Private Equity) and other investors in China announced an ambitious plan under which more than $150 billion were to be invested over next 5 to 10 years in developing semiconductor… Read More

A Brief History of Defacto Technologies

In early 2000s, semiconductor design at RTL level was gaining momentum. The idea was to process more design steps such as insertion of test and other design structures upfront at the RTL level. The design optimization and verification were to be done at the RTL level to reduce long iterations through gate level design because changes… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center