You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Next Tuesday and Wednesday, March 13-14th, is CDNLive in Silicon Valley at the DoubleTree Hotel (which I see we are now meant to call DoubleTree by Hilton, although I still have to think twice not to call it the Red Lion, the group whose CFO at one point was Ray Bingham who was CFO and then CEO of Cadence. Trivia fact for the day).

CDNlive… Read More

There is an interview in the San Jose Mercury News with Kathryn Kranen, Jasper’s CEO. Of course the Mercury is a general newspaper and can’t expect most of its readership to have a clue what EDA is, never mind formal verification. It’s a similar problem to the one we all have when we try and explain to our families… Read More

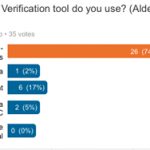

I had no idea that there was a clock domain crossing (CDC) linkedIn group but indeed there is. Richard Brabant has set up a survey to see which tools people are using.

The graph is somewhat confusing since, for example, Cadence Conformal is currently at zero but has a significant looking bar. But far and away the market leader (in this… Read More

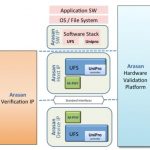

Now that the dominant approach to building an SoC is to get IP from a number of sources and assemble it into a chip, the issue of IP quality is more and more critical. A chip won’t work if the IP doesn’t work, but it is quite difficult to verify this because the SoC design team is not intimately familiar with the IP blocks since… Read More

Last May, Atrenta and TSMC announced the Soft-IP Alliance Program which uses SpyGlass and a subset of its GuideWare reference methodology to implement TSMC’s IP quality assessment program. TSMC requires all soft-IP providers to reach a minimum level of completeness before their IP is listed on TSMC online. Since TSMC … Read More

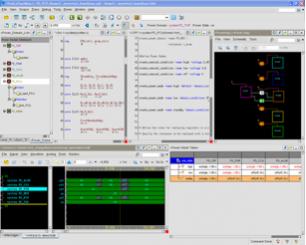

The first version of the debug platform Verdi (then called Debussy) dates back to 1996 over 15 years ago. The second version was released in 2002. And now SpringSoft is releasing the 3rd version Verdi[SUP]3[/SUP]which is a completely new generation. A tool environment like Verdi seems to need to be completely refreshed about every… Read More

CEO Forecast Panelby Paul McLellan on 03-02-2012 at 2:40 pmCategories: EDA, Events

This year’s CEO forecast panel was held at Silicon Valley Bank. Bankers live better than verification engineers, as if you didn’t know, based on the quality of the wine they were serving compared to DVCon.

This year the panelists were Ed Cheng from Gradient, Lip-Bu, Aart and Wally (and if you don’t know who they… Read More

Farm Managementby Paul McLellan on 03-01-2012 at 5:34 pmCategories: EDA

Every so often I come across a new company in EDA or one of its neighboring domains, new to me anyway, and new to SemiWiki. One such company is RunTime Design Automation (RTDA). They provide a suite of tools for managing server farms (or internal clouds which seems to be the trendy buzzword du jour). Running a few EDA scripts on a few servers… Read More

There has been a general trend for over a decade now towards the use of very fast serial interfaces instead of wide parallel interfaces. This has been driven by a number of different factors ranging from the lack of pins on an SoC, the difficulty of keeping wide parallel interfaces free of skew, limitations on printed circuit board… Read More

DVCon is next week, which I’m sure you know already if you are in verification. Of course Synopsys has a rich product portfolio in verification and verification IP (VIP) so is pretty visible at the show.

On Wednesday they are sponsoring lunch. Several Synopsys customers will talk about their view of how the verification landscape… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era